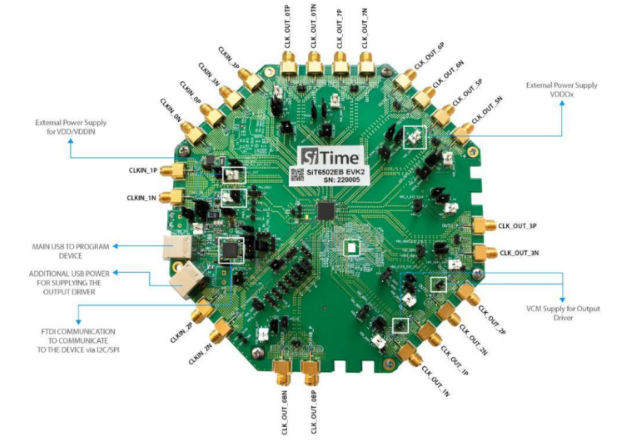

SiT6502EB 评估板 支持 SiT95147 抖动消除器/衰减器

SiT6502EB 评估板 (EVB) 硬件用户手册

1. 1. 简介

SiT6502EB 评估板 (EVB) 设计用于评估可编程SiT95147 抖动消除器/衰减器。

2. SiT6502EB 特性

由 USB 端口或外部电源供电

8 个输出的可编程 VDDO 电源可从 3.3、2.5 或 1.8 V 中选择

用于显示 SiT6502EB 电源状态信号的 LED 状态指示灯 - 可通过边缘安装访问 8 个输出中的每个输出

高带宽 SMA 连接器

4 对边缘安装 SMA 连接器,用于馈入外部差分或单端时钟

通过标准 I2C 或 SPI 接口和 Windows 托管的时钟时间主控图形用户界面,支持设备的全面灵活配置

3. SiT6502EB 支持附件

SiT6502EB 评估板随附以下附件:

SiT6502EB EVB 硬件用户手册

时钟主控软件

时钟软件时间掌握器用户手册

4. 连接器说明

表 1列出了 SiT6502EB EVB 的连接器:

连接器代号 | 说明 |

|---|---|

| Power + Control | USB Type B connectors (J3) for Device programming and +5V supply |

| Power | USB Type B connectors (J4) for +5V supply, 2-pin connectors (J80, J7) for external +5V power supply |

| Inputs | SMA connectors (J35 through J42) for receiving external clock signals |

| Outputs | SMA connectors (J43 through J62) for synthesized clock outputs |

| External FTDI supply | 2-pin connector (H13) |

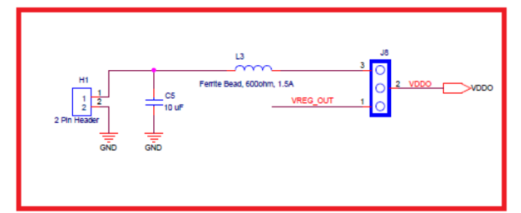

| External +3.3V (VDD Left) Input receiver supply | 2-pin connector (H1) |

| External +3.3V (VDD PLL) supply | 2-pin connector (H12) |

| External Output VDD Supply | 2-pin connectors (H2 through H11) |

| Common Mode to GND Headers in output terminations | 2-pin Headers (JSCL13 through JSCL22) |

| Output LDO Regulators Enable Inputs to GND Headers | 2-pin Headers (J2, JSCL3 through JSCL11), shorted by default for LDO outputs enabling |

| Left Supply LDO Regulators Enable Inputs to GND Headers | 2-pin Headers (J1), shorted by default for LDO outputs enabling |

| Header for internal use only | 2-pin Header (JSCL 1), shorted by default |

| Headers for I2C bus Pull-up | 2-pin Headers (JSCL 2, JSCL 12), shorted by default |

| Header | 1-pin Header (J5) |

| Header for PLL supply LDO regulator output Shut Down | 2-pin Header (J12) |

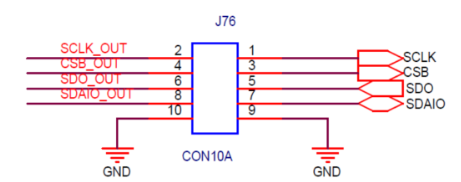

| Header for internal use only | 10-pin Header (J76) (Default Jumper position see in Figure A20) |

| PullUp vs PullDown switch Headers | 3-pin Headers (J67 through J69, J72 through J74, J75, J81, JVDD1) |

| Signals switch Header | 3-pin Header (J71) |

| PLL supply voltage source switching Header | 3-pin Header (J31) |

| PLL supply voltage levels switching Header | 3-pin Header (J32) |

| Left supply voltage source switching Header | 3-pin Header (J8) |

| Left supply voltage levels switching Header | 3-pin Header (J9) |

| FTDI supply voltages source switching Header | 3-pin Header (J78) |

| FTDI supply voltage levels switching Header | 3-pin Header (J30) |

| USB – External Power sources switching Headers | 3-pin Headers (J79, J6) |

| Outputs supply voltage source switching Header | 3-pin Headers (J10, J77, J14, J16, J18, J20, J22, J24, J26, J28) |

| Outputs supply voltage levels switching Header | 3-pin Headers (J11, J13, J15, J17, J19, J21, J23, J25, J27, J29) |

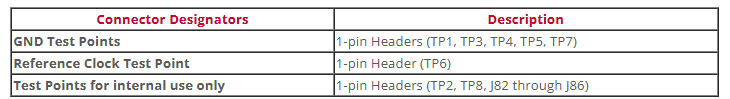

5. 测试点说明

表 2介绍了 EVB 上的所有测试点 (TP):

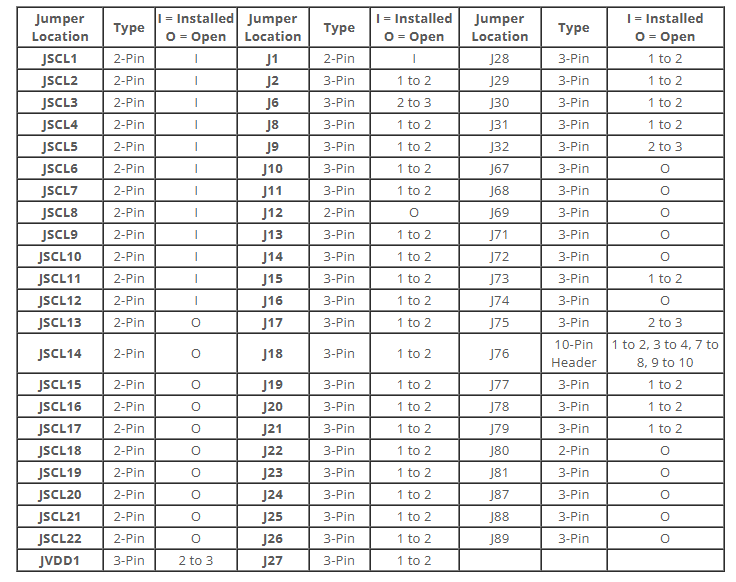

6. 跳线默认列表

表 3列出了 EVB 上跳线的默认位置:

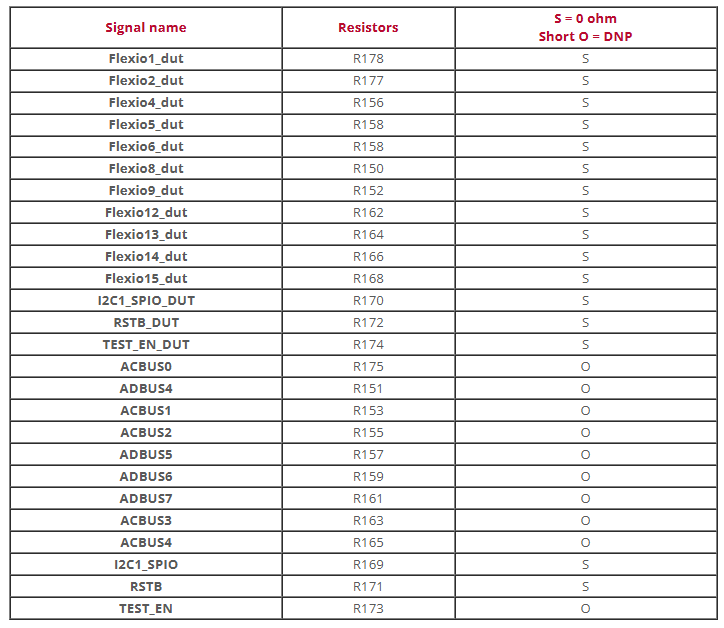

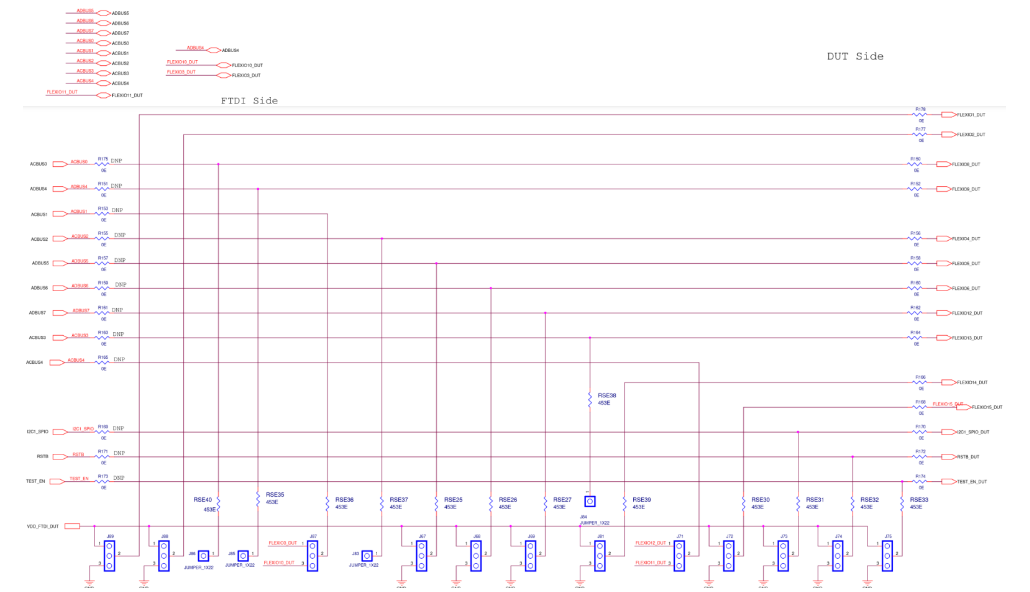

7. 从 FTDI 到 SiT95147 的默认电阻连接

表 4列出了从 FTDI 到 EVB 上 SiT95147 器件的默认电阻连接:

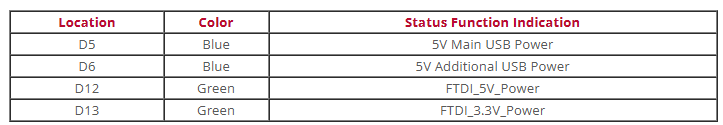

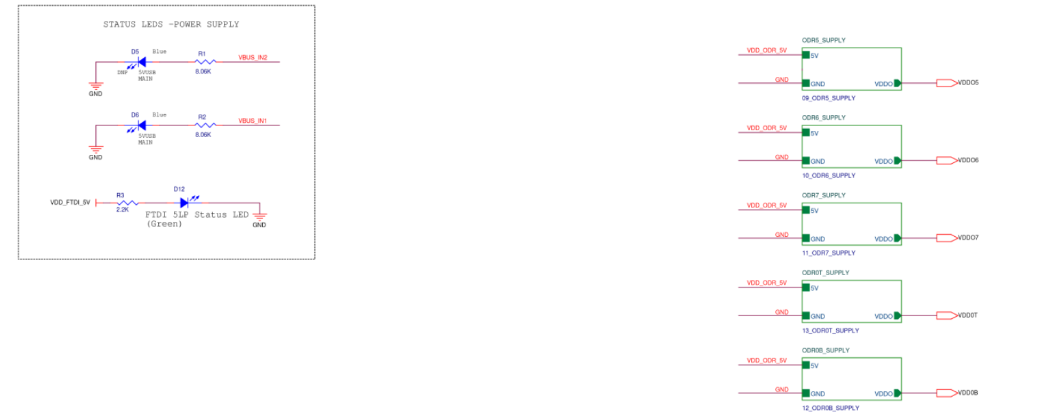

8. 状态 LED 指示灯

表 5列出了图 1 中 SiT6502EB EVB 上的状态 LED

*注:当存在相应电压时,所有 LED 都会亮起。

图 1. 状态 LED 指示灯

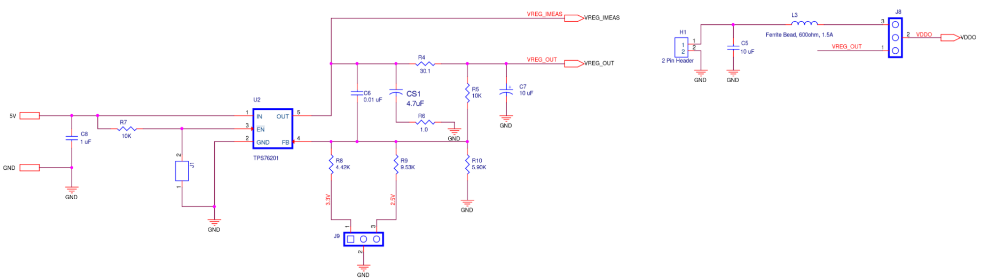

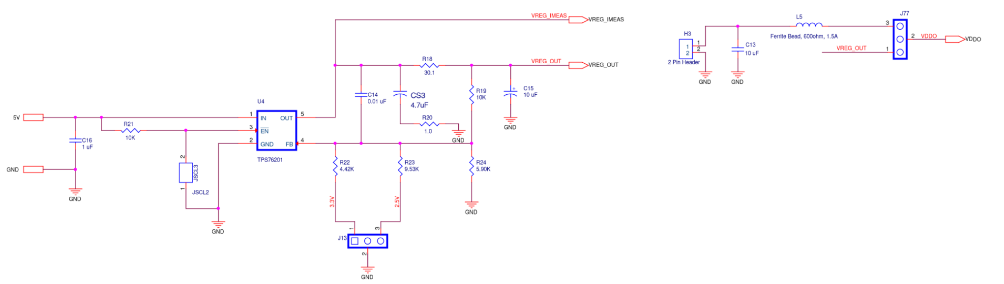

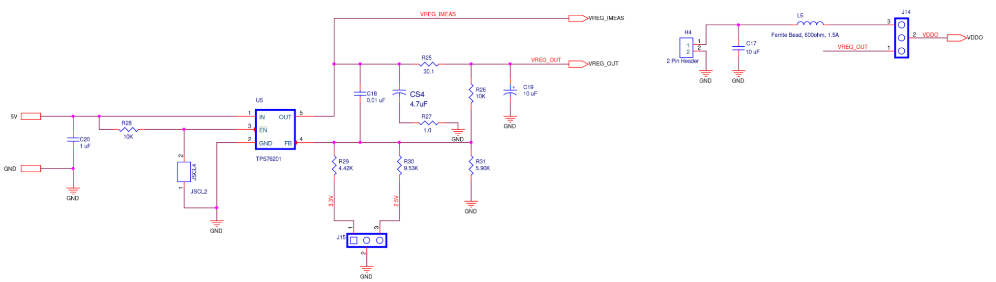

9. SiT6502EB 电源

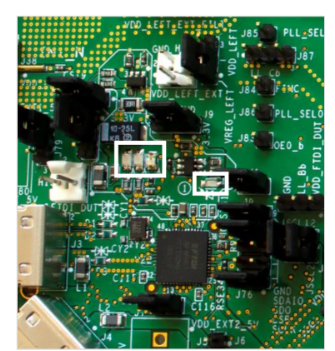

SiT6502EB 上的被测设备 (DUT) 模拟供电电压 (VDDIN) 和 DUT 输出供电电压 (VDDOx) 默认配置为 3.3 V,而 DUT PLL 的供电电压 VDD 电源配置为 1.8 V。有关 VDDIN/VDD 和 VDDOx 引脚电源电压的配置,请参阅 SiT95147 数据手册,有关 SiT95147 板载配置选项,请参阅表 6:

表 6. SiT6502EB 电源配置

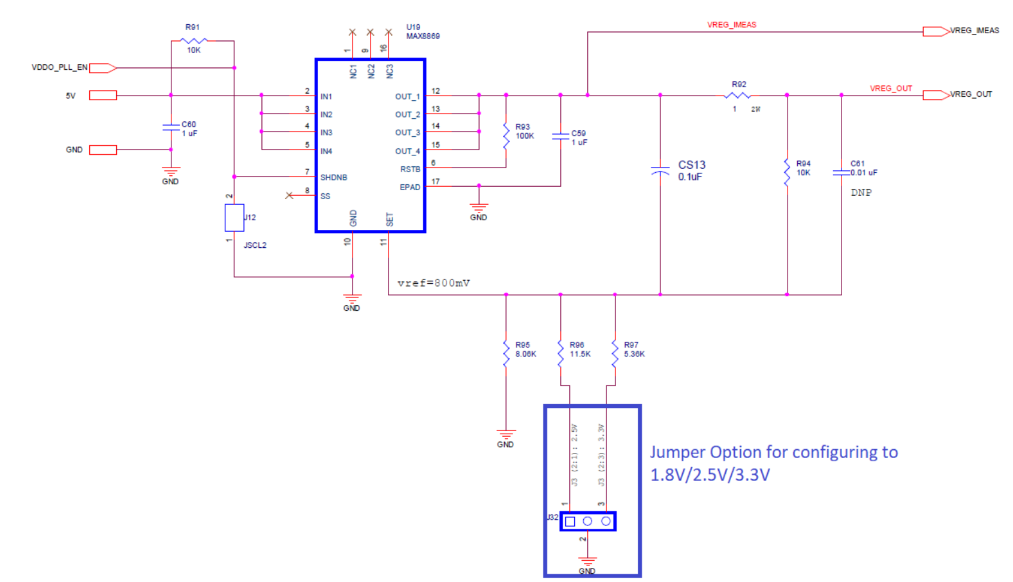

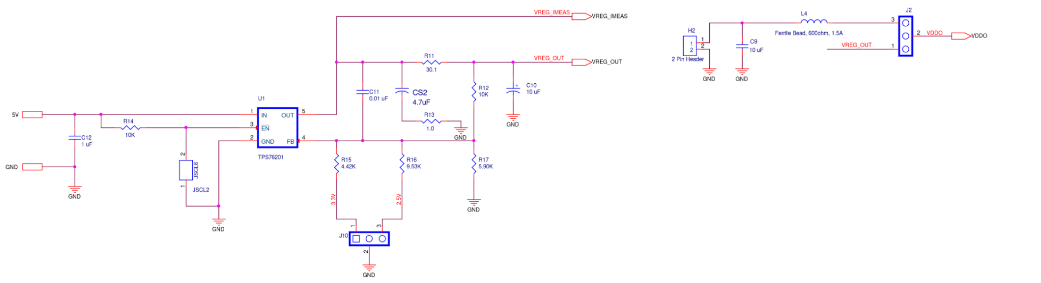

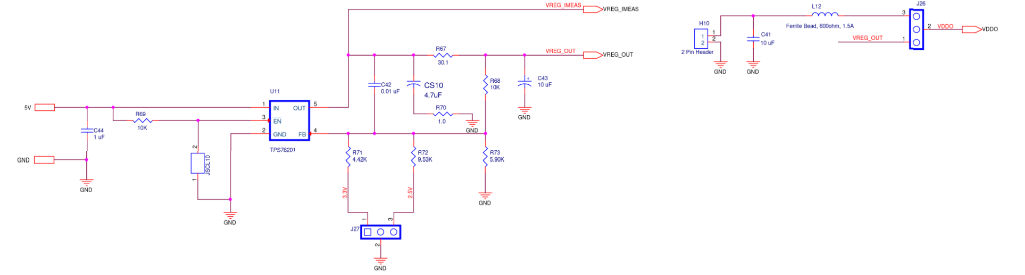

图 2. VDDIN/VDDOx 电源调节器

注:要更改 VDDIN (J9) 和 VDDOx 电源,请将相应的跳线连接至以下设置:

3.3 V - 将 3 针跳线从 1 连接到 2。

2.5 V - 将 3 针跳线从 2 连接到 3。

1.8 V - 移除跳线。如图 3所示,在旁路所有电源的板载稳压器后,可连接外部电源。

图 3. 外部电源连接规定

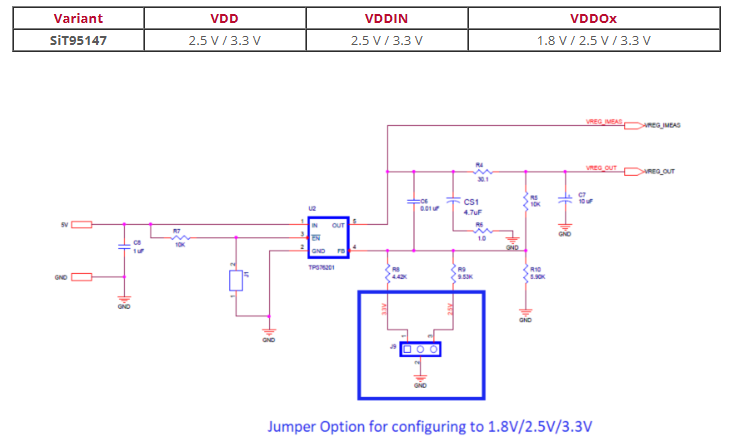

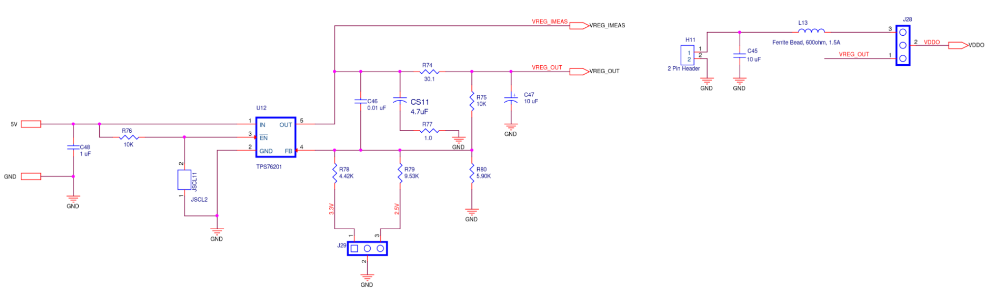

PLL 的供电电路如图 4所示。

图 4. 电源稳压器

注:要更改 VDD (J32) 电源,请将跳线连接至以下设置:

3.3V - 将 3 针跳线从 2 连接到 3。

2.5V - 将 3 针跳线从 1 连接到 2。

1.8V - 移除跳线。

10. I2C/SPI 模式连接

10 引脚接头 J76(图 5)主要用于将 SiT6503EB 配置为 I2C 和 SPI 模式(默认为I2C 模式)。

对于I2C 工作模式:

在 J76 中,SCLK_OUT 与 SCLK 短路

SDAIO_OUT 与 J76 中的 SDAIO 短路

CSB_OUT 与 J76 中的 CSB 短路

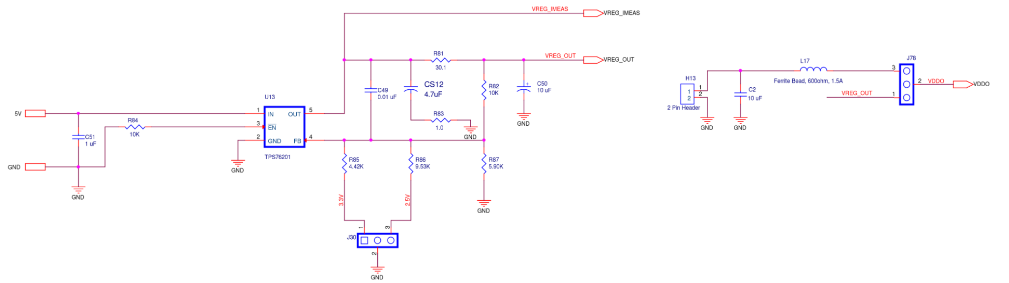

图 5. 用于 PLL 的电源稳压器

对于 SPI 运行模式:

SCLK_OUT 与 J76 中的 SCLK 短路。

SDAIO_OUT 与 J76 中的 SDAIO 短路。

CSB_OUT 与 J76 中的 CSB 短路。

SDO_OUT 与 J76 中的 SDO 短路。

JSCL1 跳线应移除。

JVDD1 跳线应从(2 至 3)变为(1 至 2)。

J73 跳线应从(1 至 2)变为(2 至 3)。

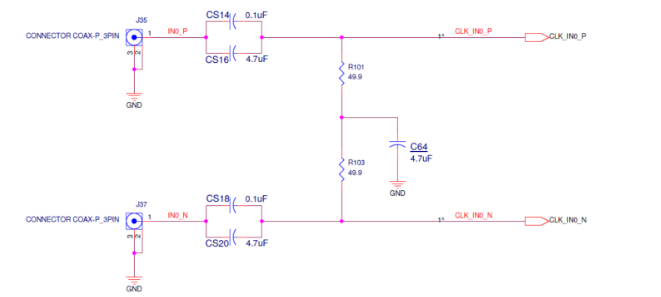

11. 时钟输入

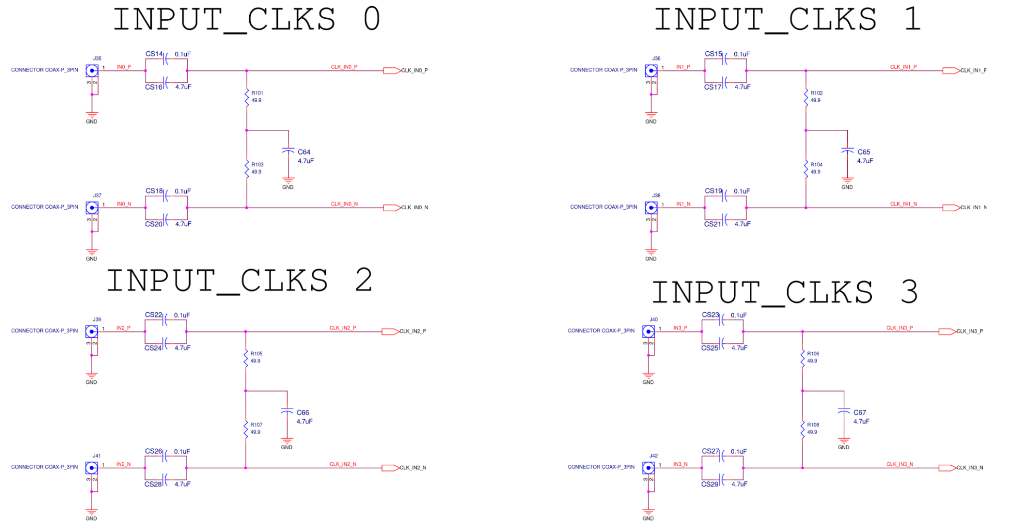

SiT6502EB 有 8 个带 SMA 连接器的输入端(4 对差分)(IN0_P、IN0_N、IN1_P、IN1_N、IN2_P、IN2_N、IN3_P、IN3_N),用于接收外部时钟信号。如下图 6所示,所有输入时钟均采用交流耦合和 50Ω 端接。这表示四个差分输入时钟对。单端时钟可通过驱动差分输入对的 “P ”端而使 “N ”输入浮动来使用。图 6显示了 4 对时钟中其中一对的输入时钟终止电路。

图 6. 输入时钟终止电路

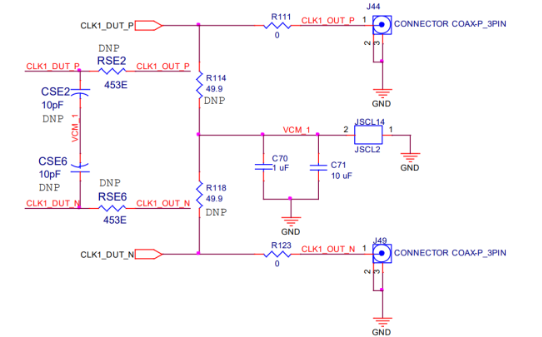

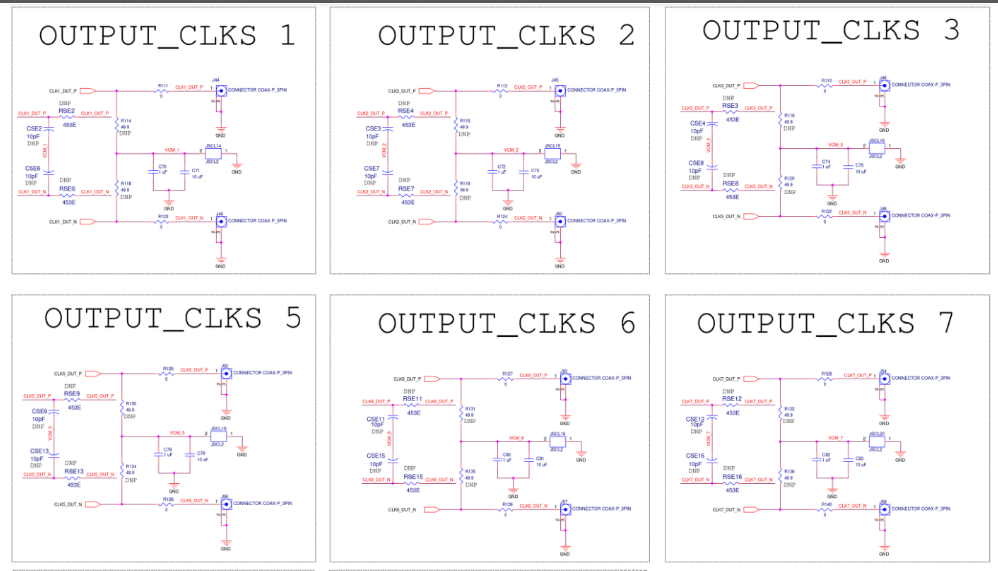

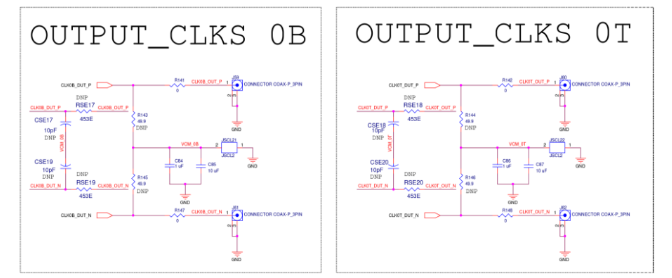

12. 时钟输出

出厂时,20 个输出驱动器(8 个差分对)中的每一个都与各自的 SMA 连接器交流耦合,这是默认配置。输出时钟终止电路如下图 7所示。如果需要直流耦合,可将相应的 0.1 uF 交流耦合电容器换成 0 Ω 电阻器。图 7显示了 8 个输出对之一的输出时钟终止电路。

图 7. 输出时钟终止电路

12.1 输出差分终端

通过更改输出端接电路,可支持 LVDS(默认配置)、LVPECL、HCSL 和 CML 差分信号类型。

12.1.1 LVDS、CML

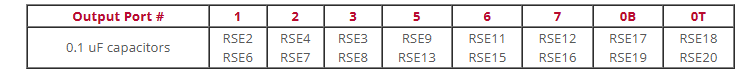

电路板出厂时支持默认差分 LVDS、CML。信号使用 0.1 uF 陶瓷电容进行交流耦合,而不是使用相应的串联电阻 RSExx(参见表 7)。

表 7. 输出端口 RSExx 电阻器

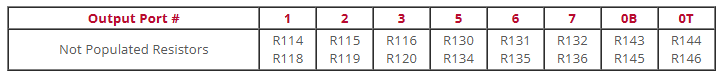

表 8所示的输出终端电阻器未填充。

表 8. 输出端口未填充电阻

12.1.2 LVPECL

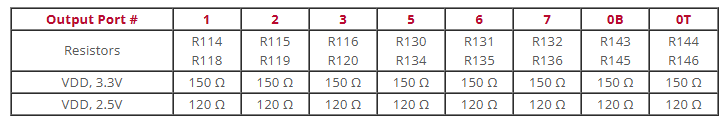

对于 LVPECL 输出配置,应使用 0.1 uF 陶瓷电容代替相应的串联电阻 RSExx(参见表 7)。表 9 列出了取决于输出驱动器 VDD 电平的终端电阻值。

表 9. LVPECL 输出端口终端电阻器

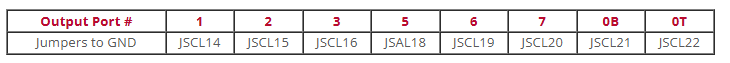

此外,确保跳线 JSCLxx 已按表 10填好,以便通向 GND。

表 10. 输出端口至接地的跳线

12.1.3 HCSL

对于 HCSL 输出配置,应使用串联电阻 RSExx(参见表 7)。每个输出端口应使用 33 Ω。请注意,在接收器侧,每对每个通道都应通过 50 Ω 端接至 GND。

13. 快速启动

在 Windows 电脑上安装 Time Master for Clocks 图形用户界面

确认已 按表 3所示安装跳线

将 USB 电缆从 SiT6502EB 的 J3 连接至电脑

启动时钟时间控制器图形用户界面

参考随附的《时钟时间控制器 SW 用户手册》,在 SiT6502EB 上配置频率计划

默认输出驱动器配置为 LVDS,输出驱动器电源配置为 3.3 V

EVB 上的默认 VDD 电源配置为 1.8V,EVB 上的默认 VDDIN 电源配置为 3.3V

EVB 上的 FTDI 芯片默认配置为I2C 通信协议。

EVB 默认配置如图 8 所示。

单 USB 电源操作的一般准则如下:

使用 USB 3.0 或 USB 2.0 端口。这些端口在 +5V 电压下可分别提供 900 mA 和 500 mA 电流。

如果使用的是 USB 2.0 端口,且电流受限,则应关闭足够的 DUT 输出稳压器,使 DUT 总电流降至 470 mA 以下。

注:USB 2.0 端口的电流可能大于 500 mA。只要标称 +5V 下降小于 10%,EVB 仍可正常工作。

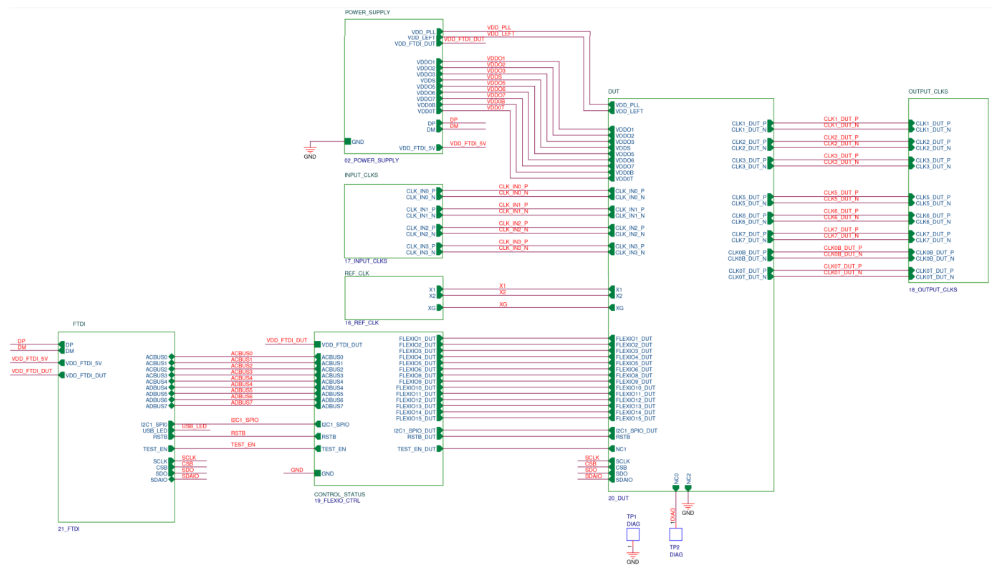

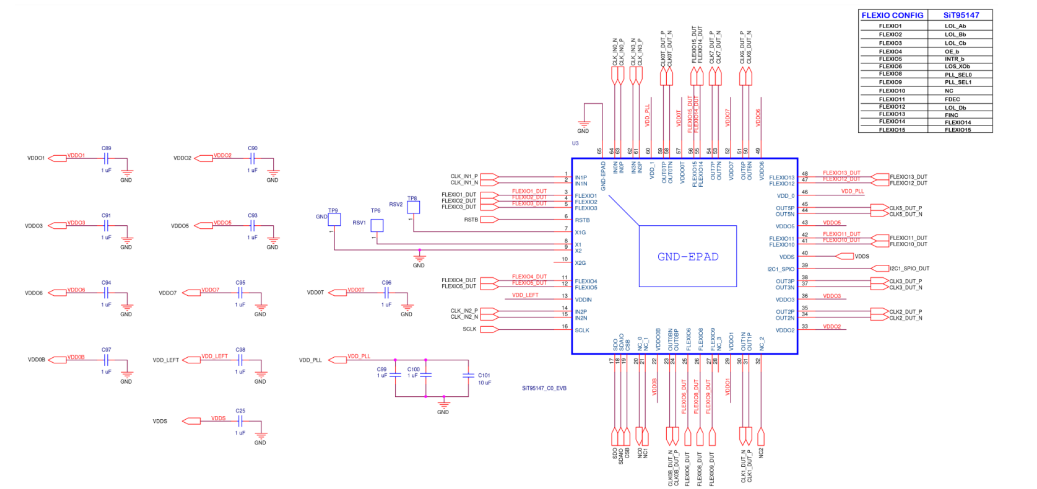

附录 A: EVB 原理图

EVB 顶层图

图 A1. SiT6502EB 顶层图

VDDS 电源

图 A2. SiT6502EB VDDS 电源图

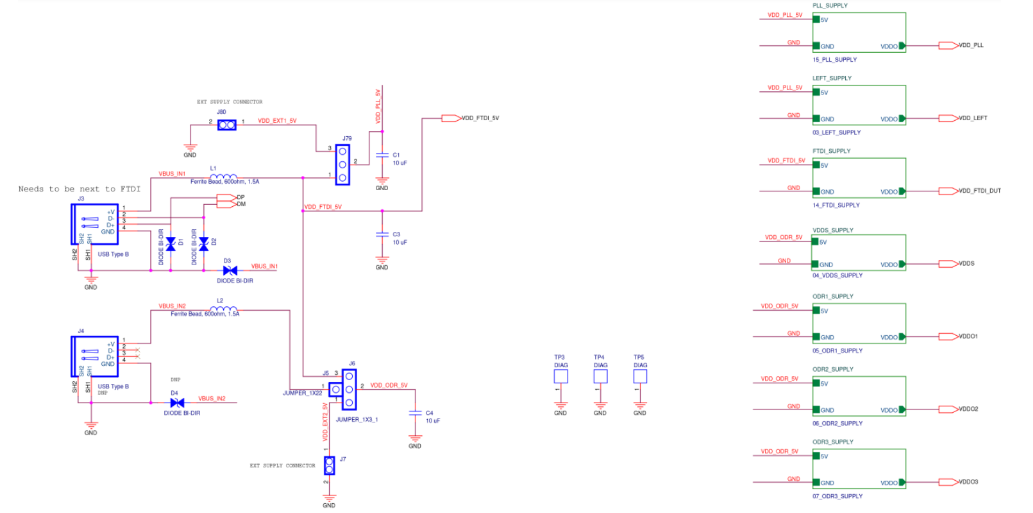

电源

图 A3. SiT6502EB 电源图

左侧电源

图 A4. SiT6502EB 左侧电源图

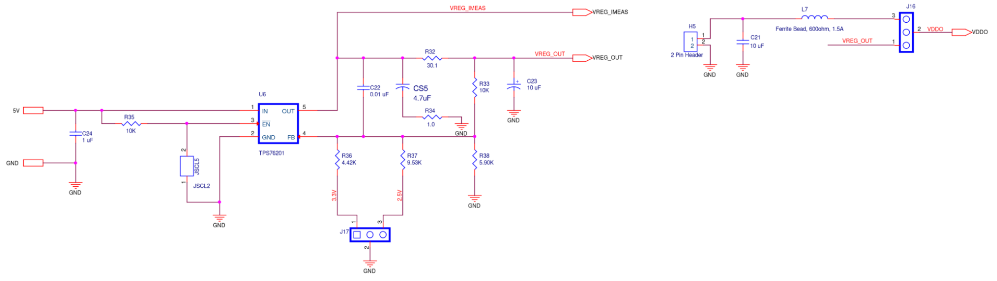

ODR1 电源

图 A5. SiT6502EB ODR1 电源图

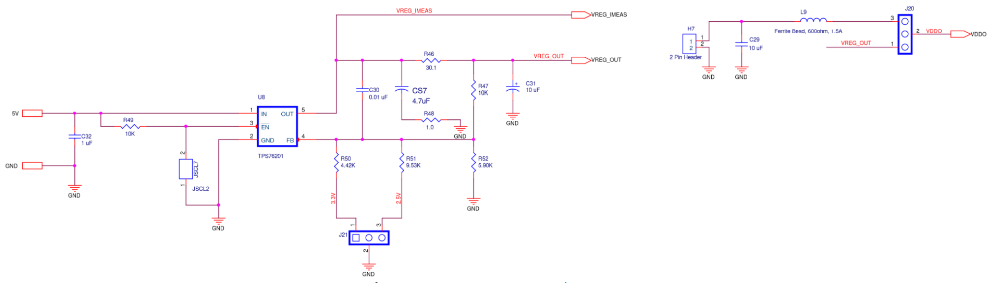

ODR2 电源

图 A6. SiT6502EB ODR2 电源图

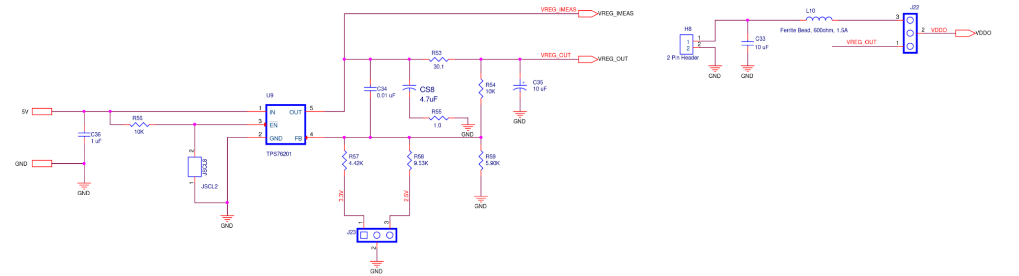

ODR3 电源

图 A7. SiT6502EB ODR3 电源图

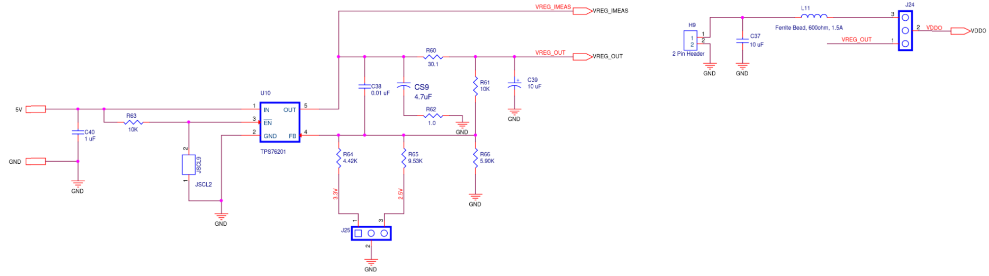

ODR5 电源

图 A8. SiT6502EB ODR5 电源图

ODR6 电源

图 A9. SiT6502EB ODR6 电源图

ODR7 电源

图 A10. SiT6502EB ODR7 电源图

ODR0B 电源

图 A11. SiT6502EB ODR0B 电源图

ODR0T 电源

图 A12. SiT6502EB ODR0T 电源图

FTDI 电源

图 A13. SiT6502EB FTDI 电源图

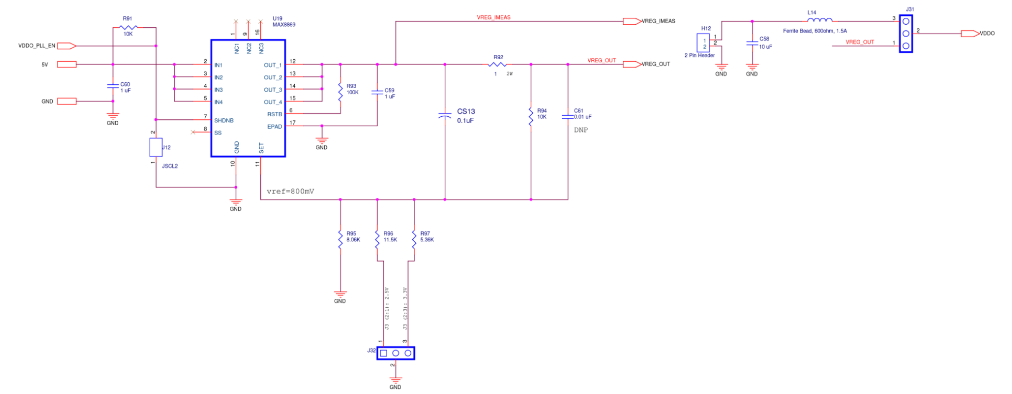

PLL 电源

图 A14. SiT6502EB PLL 电源图

输入时钟

图 A15. SiT6502EB 输入时钟图

输出时钟

图 A16. SiT6502EB 输出时钟图

状态指示灯 - 2

图 A17. SiT6502EB 状态 LED

QFN SiT95147 EVB

图 A18. QFN SiT95147 EVB 图

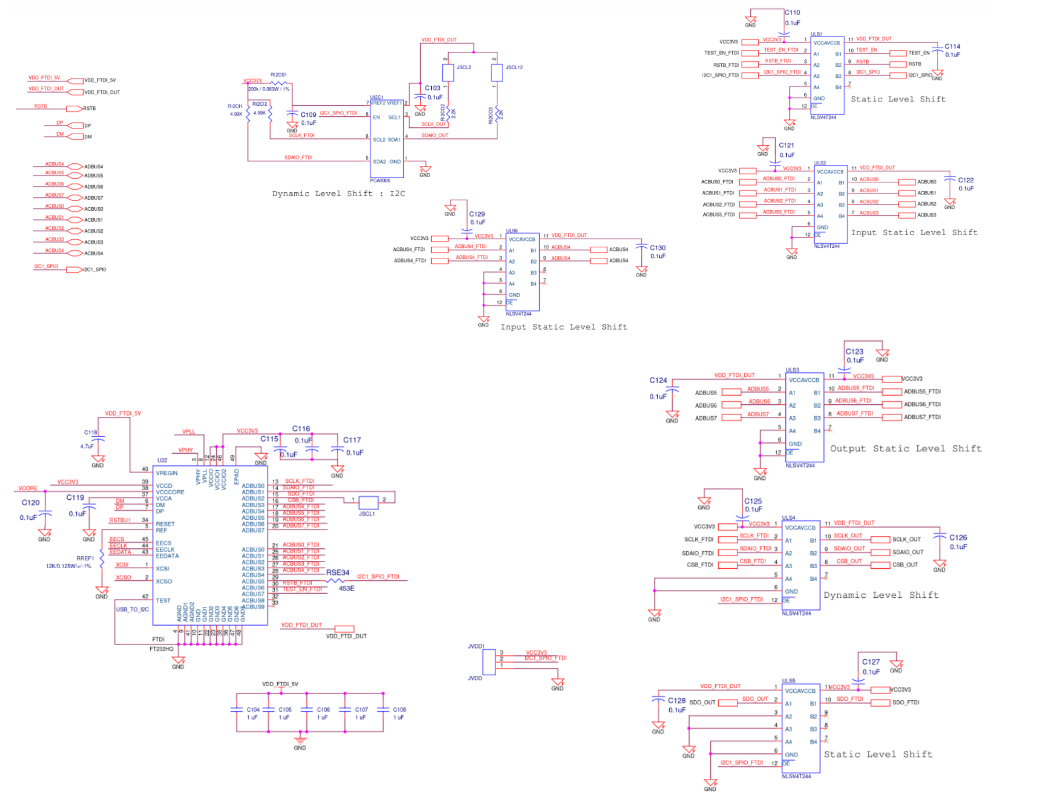

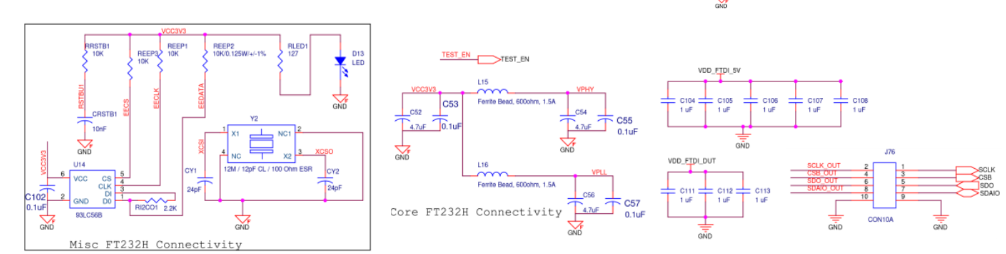

FTDI

图 A19. SiT6502EB FTDI 图

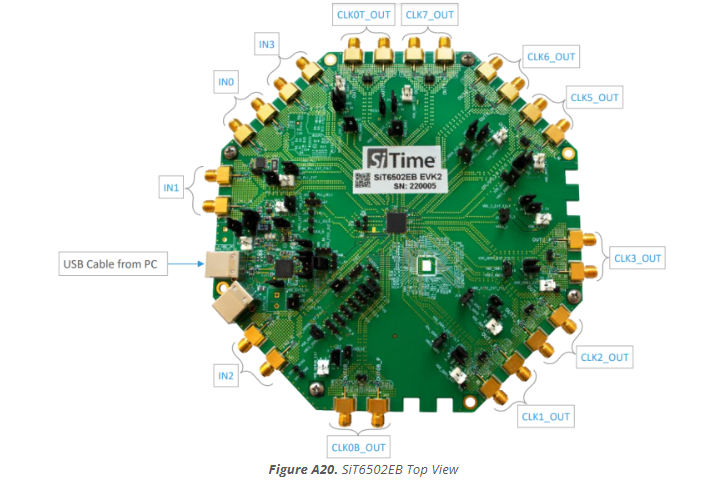

附录 B:EVB 俯视图

- MEMS振荡器为何具有较高的耐久性和可靠性2024-07-19 15:01:537500

- 深入了解MEMS辅助温度传感器为何具有 20-µK 分辨率2024-07-18 10:39:036000

- SiTime具有 40 μK 分辨率的DualMEMS 谐振器时间数字转换器2024-07-17 11:21:013600

- 深入分析低带宽锁相环的高稳定性为何受控振荡器影响2024-07-16 18:02:338800

- ±0.01ppm高精度温补振荡器SiT5501如何改变边缘网络的精确计时市场2024-01-17 00:00:008870

- ±0.1ppm高精度温补振荡器SiT7910如何为航空航天和国防提供25倍精准计时2023-03-17 10:38:231433227

- 汽车级晶振选型设计指南2022-06-28 09:14:544800

- SiTime硅晶振在SSD存储中的应用2022-05-23 09:51:424400

- 示波器的两个最重要参数之示波器宽带和采样率详解2022-04-02 13:32:204000

- SiTime推出高性能XCalibur™有源谐振器SiT14082022-02-08 09:47:598022

- 汽车级晶振为自动驾驶ADAS保驾护航2021-08-20 13:39:175884

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483