深入分析低带宽锁相环的高稳定性为何受控振荡器影响

摘要

对于低带宽锁相环(PLL),高 Q 值受控振荡器(CO)因其低增益和高稳定性而成为首选器件。本文讨论了两种不同的压控振荡器(VCXO)实现方式,即基于变容二极管的和基于锁相环的。还讨论了数控振荡器(DCXO),以在系统设计中增加灵活性和鲁棒性,同时考虑量化、更新延迟和环路滤波器实现对环路性能的影响。

一. 引言

高稳定性受控振荡器(CO)用于网络、电信、视频/音频和仪器仪表应用中的同步或抖动清理锁相环。此类锁相环通常具有非常低的带宽,例如小于 1 KHz,以从参考输入时钟中滤除大部分相位噪声和抖动。这些电路使用高 Q 值机械谐振器来实现非常低的频率控制增益和高稳定性,这对于稳定的低带宽锁相环设计是必要的。两种主要的高稳定性受控振荡器如下:

• 基于可牵引高 Q 值谐振器的压控振荡器(VCXO)

• 基于高 Q 值谐振器的数控振荡器(DCXO)

当输入到锁相环的信号中断且受控振荡器实际上处于自由运行状态时,对于需要非常严格稳定性的应用,可以提高 VCXO 或 DCXO 的固有频率稳定性。例如,SONET 和电信应用中的同步器和重定时器具有保持功能。在这种情况下,通过温度补偿技术(VC-TCXO 或 DC-TCXO)进一步稳定机械谐振器的频率,以校正温度变化引起的频率变化,或者采用恒温控制技术(VC-OCXO 或 DC-OCXO)来稳定谐振器温度,并避免由于环境温度变化而引起的频率变化。

最广泛使用的高 Q 值谐振器要么基于石英晶体,要么基于微机电系统(MEMS)谐振器[1]。这些谐振器分别依赖于石英晶体或硅材料的机械特性来实现高 Q 值。石英谐振器基于压电现象工作。当在其谐振频率对其施加机械应力时,这些谐振器会产生最大电流。相比之下,目前市售的 MEMS 谐振器使用静电激励来产生高 Q 值振荡[1]。

高稳定性 CO 用于频率控制的两种主要方法如下:

• 直接牵引机械谐振器的频率

• 使用高分辨率锁相环进行牵引

上述频率控制设备提供了不同的特性和优势,这会影响使用它们的低带宽锁相环(PLL)的设计和性能。本文分析了这些特性和优势,并研究了由此产生的权衡。

二. 压控晶体振荡器(VCXO)架构和规格

在解释不同类型 VCXO 的架构和特性之前,让我们定义如下关键的 VCXO 规格。

• 牵引范围(PR)

在标称条件下,整个输入电压范围内的频率控制范围。

• 绝对牵引范围(APR)

在包括温度、老化和电压/负载变化的全工作条件范围内保证的频率控制范围。APR 计算为 PR 减去由于任何其他因素导致的振荡器频率稳定性。

• VCO 增益(kv)

给定输入电压变化时的频率变化比率。该比率表示为 Hz/V 或 ppm/V。

• 近端相位噪声

在低于 10kHz 偏移的频率偏移处的相位噪声,通常由输入电压噪声灵敏度主导。

2.1、VCXO 架构 VCXO

使用以下列出的两种频率控制方法之一:

1. 直接牵引机械谐振器频率

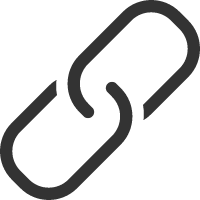

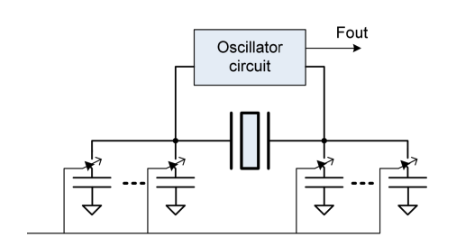

这种类型 VCXO 的一个常见示例是基于石英的振荡器,其谐振频率通过改变并联电容来控制。通常,使用变容二极管通过电压控制电容,从而产生 VCXO 器件。此示例见图 1。

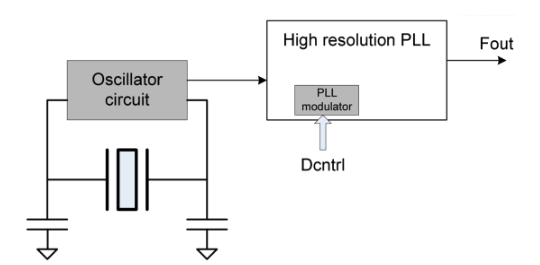

2. 使用 PLL 牵引

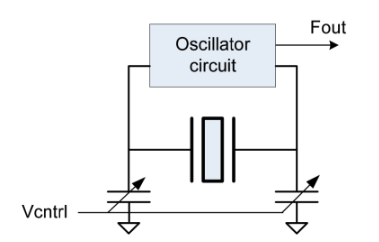

在这种架构中,稳定的振荡器输出驱动高分辨率 PLL,通常是分数 N PLL 以实现足够高的分辨率。PLL 调制器以模拟方式通过模数转换器(ADC)驱动。此架构见图 2。

图 1:基于牵引谐振器频率的 VCXO

图 2:基于不可牵引谐振器和高分辨率 PLL 的 VCXO

2.2 基于变容二极管的 VCXO

这些 VCXO 使用变容二极管来“牵引”基于石英的振荡器的频率,并已在许多应用中广泛使用。然而,它们的使用需要仔细权衡噪声、APR 和 Kv。通常,对于目标 APR,选择最低的 Kv 以最小化相位噪声影响并提高 PLL 稳定性更好。适应大于+/-100ppm 的牵引范围可能会对相位噪声性能或器件的可靠性/质量产生不利影响。Kv 相对于控制电压的线性度在 10%范围内,这会在整个工作范围内影响 PLL 带宽和稳定性。

2.3 基于 PLL 的 VCXO

基于 PLL 的 VCXO 使用由高稳定性振荡器(如基于 MEMS硅晶振 或石英的振荡器)驱动的高分辨率 PLL,如图 2 所示。频率控制功能通过 ADC 实现,该 ADC 将输入电压数字化并驱动分数 N PLL 调制器。这种架构具有以下优点:

• Kv 线性度为 0.1%至 1%很容易实现

• 可以实现宽牵引范围(> 1000ppm),而不会影响 MEMS硅晶振 或基于石英的振荡器的质量

然而,此类 VCXO 确实需要额外的 ADC 和分数 PLL 电路。ADC 数字分辨率通常设计为小于交流电路的热噪声。ADC 之后是低通滤波器,以最小化热噪声和量化噪声。由于热噪声的抖动效应,整个电路实际上允许无限分辨率。因此,从应用的角度来看,在频率控制分辨率方面,直接模拟控制和使用此类 ADC 之间没有区别。

ADC 噪声对近端相位噪声的影响取决于牵引范围。牵引范围越高,输出对输入噪声越敏感。对于低牵引范围,在±50ppm 或更低的范围内,噪声影响通常最小,这意味着近端相位噪声主要由振荡器相位噪声主导。

Vin 噪声影响与牵引范围成正比增加,牵引范围每增加一倍,大约增加 6dB。对于基于变容二极管的石英 VCXO 也是如此。因此,在这两种类型的 VCXO 中,近端相位噪声和牵引范围之间存在权衡。

3. 低带宽锁相环中的压控晶体振荡器(VCXO)

低带宽锁相环(PLL)可以通过两种主要方式实现:

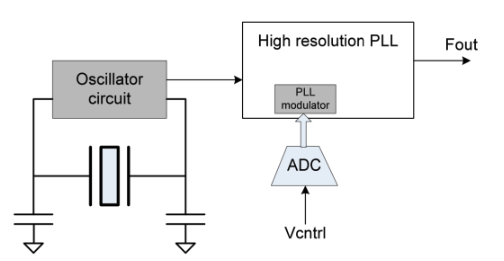

使用相位检测器和/或电荷泵,然后接极低带宽的模拟环路滤波器,如图 3 所示。由于带宽低,环路滤波器的 R 和 C 值通常非常大。

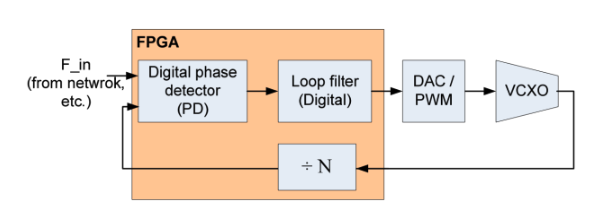

使用具有数字输出的相位检测器。在 FPGA 中实现环路滤波器,并使用数模转换器(DAC)来驱动 VCXO,如图 4 所示。 第二种方法更灵活,因为可以通过软件轻松修改滤波器。然而,它需要额外的 DAC 电路,这可以是一个简单的脉冲宽度调制器(PWM)电路,后面接一个电阻 - 电容(RC)滤波器。

图 3:带有 VCXO 和模拟环路滤波器的低带宽 PLL

图 4:带有 VCXO 和数字环路滤波器的低带宽 PLL

4. 数控晶体振荡器(DCXO)

架构 DCXO 也可以通过两种方式实现。

如图 5 所示,通过数字切换一系列并联电容来牵引石英谐振器的频率。

使用高分辨率 PLL 从属于高 Q 值振荡器。如图 6 所示,频率控制功能是通过直接驱动 PLL 反馈分频器或分数 N PLL 调制器的数字输入来实现的。

图 5:基于谐振器牵引的 DCXO

图 6:基于高分辨率 PLL 的 DCXO

DCXO 在优化关键控制振荡器参数方面具有最大的灵活性。DCXO 在低带宽 PLL 中的优势在于:

• 极其线性的特性。很容易实现优于 1%的线性度,而通过变容二极管获得的线性度为 5%至 10%。

• 用户可编程的 Kv Kv 和 APR 之间无需权衡。

• 可牵引的谐振器在温度变化时往往变得不太稳定。

• 这需要更大的牵引范围和 Kv 以实现目标 APR 由于输入电路的模拟噪声,不会降低近场相位噪声

• 在牵引范围和相位噪声之间无需权衡 无需用于数模转换的额外电路或板载模拟滤波器

此外,DCXO 允许使用 FPGA 或微控制器(uC)动态控制环路带宽。例如,可以将带宽设置得更高以减少锁定时间,然后降低以改善跟踪动态和稳定性。

然而,使用 DCXO 进行设计时,需要注意使用 VCXO 时不相关的问题。

5. 将 DCXO 用于低带宽 PLL

DCXO 的输出频率通过向设备的某些内部寄存器写入来控制。在 PLL 设计中需要考虑的 DCXO 特性如下:

• 频率控制分辨率

• 频率更新速率

• 频率更新延迟

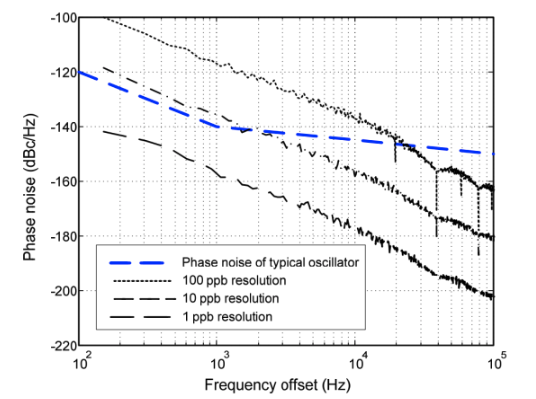

频率分辨率和更新速率的组合决定了由于量化噪声引起的附加相位噪声。图 7 显示了对于 10 MHz DCXO 不同分辨率的近载波相位噪声的仿真结果。此仿真假设更新速率为 25000 次/秒。如图所示,在 100 ppb(1e-7)的 DCXO 分辨率下,在低于 10 kHz 的频率偏移处,附加相位噪声开始占主导地位。对于 10 bbp(1e-8)的分辨率,DCXO 量化噪声的影响低于或略高于大多数基于 MEMS振荡器 或石英振荡器的固有相位噪声。在这个水平上,DCXO 量化噪声对相位噪声性能几乎没有影响。如今的现代 DCXO,例如来自 SiTime 的高精度 SiT3907 [2],很容易提供 1 ppb 或更好的分辨率,从而有效地消除了对输出相位噪声的任何量化影响。

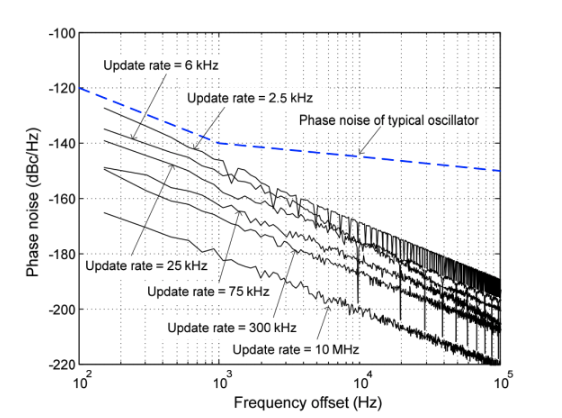

更新速率也可能是最终相位噪声的重要因素。通常,低更新速率会导致来自鉴相器和环路滤波器的误差信号由 DCXO 积分很长时间,从而导致更高的相位噪声。图 8 中的仿真显示了分辨率为 1 ppb 的 DCXO 的更新速率的影响。该仿真表明,即使更新速率在 2500 次/秒的范围内,也足以确保量化噪声不影响整体相位噪声。

图 7:不同频率 DCXO 控制分辨率下的量化引起的相位噪声

图 8:DCXO 更新速率对近载波相位噪声的影响

使用 DCXO 时,还需要考虑低带宽 PLL 的稳定性。除了环路滤波器响应外,DCXO 的更新速率和延迟会影响环路的整体稳定性。为了确保稳定运行,通常更新速率和更新延迟的倒数应至少比目标环路带宽高 10 倍。这意味着对于 1 kHz 的环路带宽,更新速率应高于 10 kHz,更新延迟应短于 100 us。幸运的是,有多个来源 [2] 可以提供能够支持此类规格的 DCXO。DCXO 输出频率可以用离散步长控制。这就引出了一个问题,即一旦 PLL 环路处于锁定状态,频率误差会是多少。这与 DCXO 分辨率和更新速率有关。实际上,低带宽 PLL 环路将在 DCXO 的输入处产生高斯噪声。

DCXO 对该噪声进行平均。频率误差可以计算为 DCXO 输入处的量化噪声除以频率误差平均次数的平方根。例如,对于分辨率为 1 ppb 且更新速率为 25000 次/秒的 DCXO,1 秒间隔内量化引起的频率误差为:

1ppb / sqrt(25000) = 0.006ppb。

在更长的时间间隔内,频率误差甚至会进一步降低。这种低水平的频率误差允许此类 DCXO 用于要求严格频率锁定的苛刻应用,例如电信。

使用 DCXO 时的另一个实现问题是鉴相器的选择。两个有吸引力的选项是:

• 使用能够在输出频率速率下工作的高速鉴相器(PD)

• 将输入和输出路径除以鉴相器,并使用低速鉴相器

在这两种情况下,PD 之后都跟着数字环路滤波器。在第一种选项中,PD 的输出需要数字化并传递给滤波器。尽管数字化器所需的位数不高,但它必须以相当高的速率运行。第二种选项允许使用更慢的数字化器,这可能更容易实现。在这种情况下,数字化器的速率必须至少比环路滤波器带宽高 10 倍,以最大程度减少对环路稳定性的影响。

6. 结论

基于锁相环(PLL)的压控晶体振荡器(VCXO)和数控晶体振荡器(DCXO)在牵引范围和灵活性方面具有优势,尽管它们需要精心设计高分辨率的 PLL。更具体地说,DCXO 允许为高性能同步和抖动清除灵活地全数字实现低带宽 PLL。如今的 DCXO 提供足够高的更新速率和分辨率,以确保任何对近端相位噪声的量化影响都可以被安全地忽略。

- MEMS振荡器为何具有较高的耐久性和可靠性2024-07-19 15:01:537400

- 深入了解MEMS辅助温度传感器为何具有 20-µK 分辨率2024-07-18 10:39:035900

- SiTime具有 40 μK 分辨率的DualMEMS 谐振器时间数字转换器2024-07-17 11:21:013500

- 深入分析低带宽锁相环的高稳定性为何受控振荡器影响2024-07-16 18:02:337100

- ±0.01ppm高精度温补振荡器SiT5501如何改变边缘网络的精确计时市场2024-01-17 00:00:008770

- ±0.1ppm高精度温补振荡器SiT7910如何为航空航天和国防提供25倍精准计时2023-03-17 10:38:231423227

- 汽车级晶振选型设计指南2022-06-28 09:14:544600

- SiTime硅晶振在SSD存储中的应用2022-05-23 09:51:424300

- 示波器的两个最重要参数之示波器宽带和采样率详解2022-04-02 13:32:203900

- SiTime推出高性能XCalibur™有源谐振器SiT14082022-02-08 09:47:597822

- 汽车级晶振为自动驾驶ADAS保驾护航2021-08-20 13:39:175684

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483