解析SiTime如何利用可编程振荡器增强FPGA的系统

一、摘要

当今的 FPGA 是包含许多功能模块的复杂系统,通常使用多个时钟来驱动不同的模块。系统设计人员必须决定如何结合外部振荡器和内部资源以实现最佳的时钟树设计。本文将讨论当今满足时钟速度和抖动要求的可用选项,重点关注作为基于 FPGA 系统的定时参考的可编程时钟振荡器。主题包括高分辨率频率选择带来的灵活性、EMI 降低技术以及基于 FPGA 的抖动清除器。

二、引言

复杂的 FPGA 包含大量的功能模块或单元,它们需要相互通信以执行各种复杂的操作。除了基本的逻辑阵列外,FPGA 还包括内部存储器(RAM)、DSP 模块、处理器、用于定时生成的锁相环(PLL)和延迟锁相环(DLL)、标准 I/O、高速数字收发器和平行接口(PCI、DDR 等)。

许多设计使用多个时钟来驱动不同的模块,每个模块可能需要不同的频率。这些时钟通常是使用外部振荡器和内部 PLL 及 DLL 的组合生成的,具体取决于时钟速度和抖动要求。某些功能的时钟速度由应用决定,而设计人员可能为系统的其他部分选择频率。

二、 多种时钟频率

与 I/O 接口相关的时钟需要以行业标准频率运行,以确保不同系统之间的互操作性。例如,PCI Express 为 100 MHz,SATA 为 75 MHz,PCI 为 33.333 MHz。

用户通常可以为驱动处理器或状态机引擎的时钟选择频率。这种灵活性允许设计人员选择一个能优化速度、功率或资源使用的频率。

在优化速度时,使用尽可能高的频率来最大化每秒的操作数似乎很简单。然而,时钟周期抖动必须足够低,以使最小时钟周期大于设计中的关键时序路径。

FPGA 中的内部 PLL 可用于从较低频率的外部参考振荡器合成较高频率的时钟。如果 PLL 具有高频率分辨率和低抖动,这可能是频率选择的有效方法。当由简单的外部振荡器驱动时,低噪声、分数 N PLL 可以满足大多数规格。

然而,许多 FPGA 使用带有环形压控振荡器(VCO)的整数 PLL,因为它们易于设计且功耗极低。这种类型的 PLL 的问题在于频率分辨率和抖动之间的权衡。

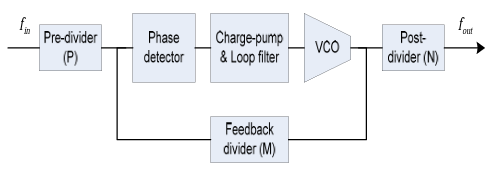

典型的整数 PLL 包括预分频器(P)、反馈分频器(M)和后分频器(N),如图 1 所示。输出频率由公式 1 定义。

图 1. 典型整数 PLL 的框图

虽然输出抖动取决于参考时钟和内部 VCO 的相位噪声,但内部 VCO 的贡献通常占主导地位。PLL 的带宽越高,VCO 相位噪声越低,整体抖动越低。

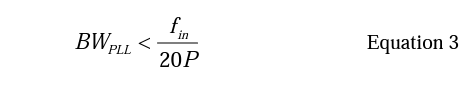

PLL 的最大带宽定义为预分频比的函数,如下所示:

在指定实际 PLL 时通常使用的更保守的带宽值由公式 3 给出:

通常希望增加带宽以改善抖动。一个问题是,通常需要较大的 P 值才能实现足够高的频率分辨率,从而限制了 PLL 的最大带宽。

三、优化PLL设计

一种既能实现高频率分辨率又能降低抖动的方法是使用可编程振荡器作为外部参考。这对内部 PLL 的要求较低,同时能提供所需的性能。可编程外部振荡器可以使用更高的频率参考,这可以降低所需的预分频比,从而实现更高的 PLL 带宽。

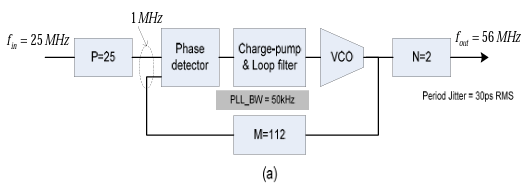

例如,考虑一个需要 56 MHz 时钟且均方根抖动为 10 ps 的应用。图 2 展示了两种设计,一种使用标准的 25 MHz 参考,另一种使用来自可编程振荡器的非标准 28 MHz 参考。

设计 a 需要较大的 P 值,导致带宽为 50 kHz(通过公式 3 计算得出)且抖动为 30 ps,这不符合规格。设计 b 利用频率可编程性选择输入频率,使得预分频比为 1,从而实现 1.4 MHz 的 PLL 带宽。均方根抖动小于 10 ps,满足规定要求。

可编程振荡器可以包括石英晶振或硅 MEMS 谐振器,但基于 MEMS 的振荡器的优势在于能够以各种行业标准塑料封装形式提供,并具有任何所需的输入频率。它们为满足要求苛刻的 FPGA 应用的抖动要求提供了经济有效的解决方案。

图 2. 两种 PLL 设计:(a) 标准频率参考时钟和 (b) 灵活频率参考时钟,允许更高的 PLL 带宽和更低的抖动

四、EMI 降低

关于振荡器的一个潜在问题是产生不必要的电磁干扰(EMI)。可编程振荡器可以整合有效降低振荡器所发射 EMI 的功能。对于 FPGA 设备,有两个有用的选项是边沿速率调整和扩频时钟(SSC)[2]。

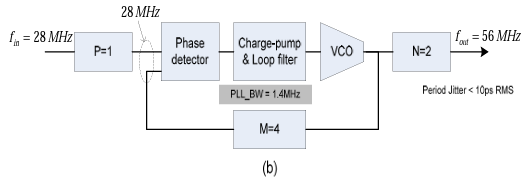

边沿速率调整,即增加时钟信号的上升和下降时间,可降低特定电路中时钟走线辐射出的高阶时钟谐波所产生的 EMI。时钟信号的峰值保持不变,避免了使用滤波器降低 EMI 时所经历的电压摆幅降低。图 3 显示了时钟谐波的幅度与上升时间的函数关系,证明了边沿速率调整在降低高阶谐波产生的 EMI 方面的有效性。假设下降时间等于上升时间,提供对称信号。

图 3. 作为上升/下降时间函数的时钟信号谐波幅度

有两种增加上升/下降时间的方法。第一种,增加负载电容,其缺点是也会增加电流消耗。可编程振荡器能够选择调整输出电流驱动,这种方法不会影响电流消耗。这种方法更可取。

虽然边沿速率调整可能有效,但它一次只能在一个电路上起作用,并且仅对时钟走线辐射出的时钟谐波起作用。此外,对于具有高速时钟的系统,可能无法充分调整上升/下降时间以实现所需的 EMI 降低。

SSC 是一种 EMI 降低技术,通过将时钟信号的能量分布在更大的频率范围内,降低了时钟树和与该树同步的数据线路所发射的峰值电磁辐射。这降低了给定频率下的峰值功率,对主载波频率和高次谐波均有效。时钟频率越高,EMI 降低效果越显著。这使得 SSC 对于高频应用非常理想。

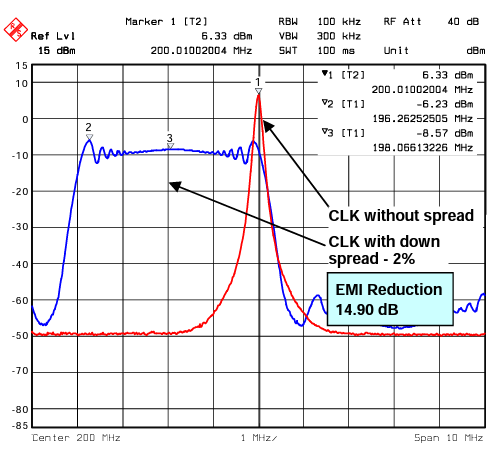

频率扩展选项包括中心扩展(围绕载波频率居中)或向下扩展,其中调制集中在标称频率以下。图 4 展示了具有 2%向下扩展的 SSC 调制示例。

图 4. SSC 调制以降低 EMI

五、系统内频率编程

可编程振荡器能够使用数字控制在系统内动态地对频率进行编程。此类器件的一个应用是在网络、电信、视频/音频和仪器仪表应用中的抖动清理。这种数字可控振荡器(DCXO)通过直接驱动锁相环反馈分频器或分数 N 锁相环调制器的数字输入来实现卓越的频率控制。[1]

由 FPGA 驱动的 DCXO 能够实现环路带宽的动态控制。例如,可以将带宽设置得更高以减少锁定时间并改善跟踪动态,或者将其设置得更低以获得更好的抖动清理性能。

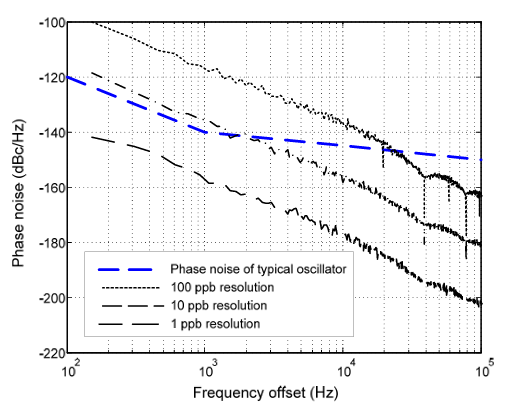

在设计 DCXO 时,有几个参数很重要:频率分辨率、更新速率和更新延迟。DCXO 的量化噪声与频率分辨率和更新速率有关,并且应远低于振荡器的固有相位噪声。如图 5 所示,在 25,000 次/秒的更新速率下,1 ppb 的分辨率导致 DCXO 产生足够低的相位噪声。

图 5. 不同频率分辨率的 DCXO 在 25 kHz 更新速率下的量化引起的相位噪声

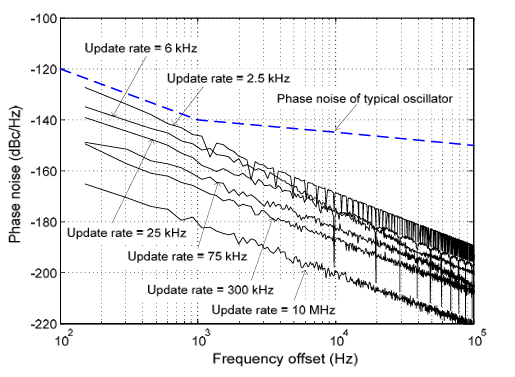

需要考虑更新速率对最终相位噪声的贡献。通常,低更新速率会导致来自相位检测器和环路滤波器的任何误差信号在更长时间内由 DCXO 积分,从而导致更高的相位噪声。对于分辨率为 1 ppb 的 DCXO,如图 6 中的数据所示,低至 2500 次/秒的更新速率可以被容忍,而不会对相位噪声产生不利影响。如今可用的高精度 DCXO 可以提供 1 ppb 或更好的分辨率,即使在相对较低的更新速率下也能有效消除对输出相位噪声的任何量化影响。

图 6. 频率分辨率为 1 ppb 的 DXCO 的更新速率对相位噪声的影响

DCXO 的更新速率和延迟有助于环路滤波器的整体稳定性。当更新速率和更新延迟的倒数都至少比目标环路带宽高 10 倍时,环路将是稳定的。这意味着对于 1 kHz 的环路带宽,更新速率应高于 10 kHz,更新延迟应短于 100 µs。具有这些规格的 DCXO 很容易获得。

六、抖动清除器

当锁定到嘈杂的系统时钟时,通常需要抖动清除技术,以生成具有低相位噪声和低抖动的稳定时钟信号。 同步或抖动清除 PLL 的一个重要组件是具有模拟 (VCXO) 或数字 (DCXO) 频率控制的高精度振荡器。

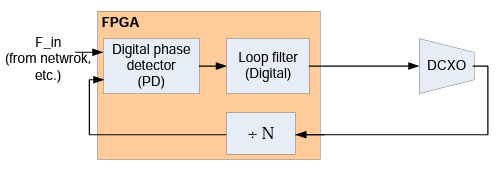

图 7:基于 FPGA 和 DCXO 的抖动清除器解决方案的实现框图

当今的高性能 DCXO 可以设计为充分降低量化噪声,使其能够成为低带宽锁相环的解决方案。仅使用 FPGA 和 DCXO 芯片已成功实现抖动清理,如图 7 所示,证明了这一概念。

七、总结

具有分数 N 锁相环的可编程振荡器可作为 FPGA 的外部参考时钟良好运行。可编程输入频率的优势使得设计具有极低抖动的锁相环成为可能。可编程性使其易于添加诸如边沿速率控制和 SSC 以降低 EMI 或数字控制以提高稳定性等功能来优化系统性能。将 FPGA 与最先进的可编程 DCXO 一起使用,具有成本效益高且参数可高度配置的额外优势,是针对有噪声的时钟参考的抖动清理解决方案。

了解更多高精度温补振荡器的信息

了解更多MEMS振荡器选型手册的信息

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483