4-16A 相位抖动方法

用于串行解串应用的反向时钟抖动分析现代方法

在快节奏的高速数据通信领域,准确的参考时钟(refclk)抖动分析的重要性怎么强调都不为过。几十年来,业界一直依赖于使用 12 kHz 至 20 MHz 砖墙滤波器分析参考时钟抖动的传统方法。然而,随着更高的数据速率和更复杂的系统的出现,这种方法已经过时,导致现代串行解串器(SerDes)应用的性能不理想。

在本文中,我们将探讨传统方法的局限性,并介绍一种新的实用方法,它有望提高系统性能,简化 SerDes 应用中的 refclk 选择。

反向时钟抖动分析的演变--传统方法

自 1992 年建立以来,用于分析反向时钟抖动的传统 12 kHz 至 20 MHz 滤波器一直是评估定时元件的基石。这种方法最初是为了支持 SONET OC-48 的 2.488 Gbps 数据速率而开发的,它将指定频率范围内的 refclk 相位噪声整合在一起,以量化相位抖动。多年来,这种方法为业界提供了良好的服务,确保了各种应用的兼容性和性能。

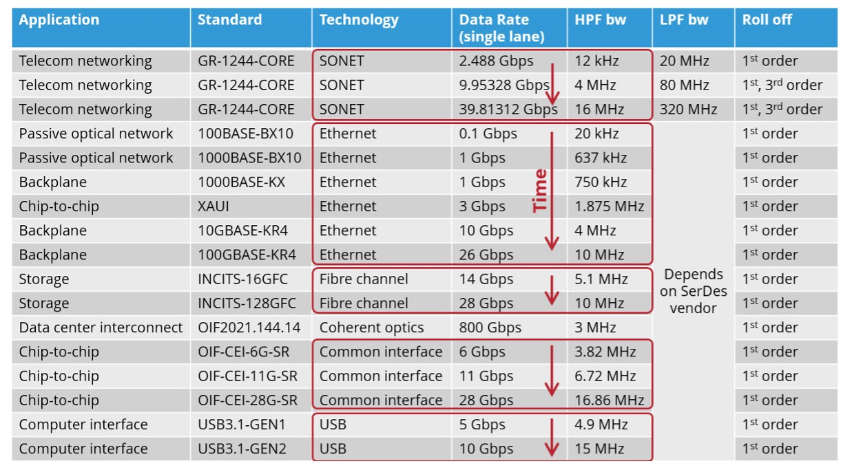

然而,自 1992 年以来,高速数据通信领域发生了翻天覆地的变化。现代系统以更高的数据速率运行,抖动预算也变得越来越严格。12 kHz 至 20 MHz 滤波器的 “一刀切 ”方法已不足以满足当今高速 SerDes 应用的各种特定要求。

反向时钟抖动分析传统方法的局限性

传统方法存在几个关键问题:

不正确的滤波器角频率: 12 kHz 至 20 MHz 滤波器并非普遍适用。不同的应用对抖动滤波器的要求各不相同,使用通用滤波器会导致不准确的相位抖动预算。

不切实际的砖墙式滤波器: 真实系统不使用砖墙式滤波器。相反,它们使用的滤波器具有逐渐衰减的特性,这对系统的总抖动有很大影响。

忽略混叠相位噪声: 传统分析忽略了混叠相位噪声,这是实际系统中的一个重要因素。这种忽略会导致严重低估实际观察到的实际相位抖动。

重大误差: 由于现代系统的抖动余量更小,数据速率更高,因此即使是抖动测量中的微小误差(几十飞秒级)也会对当今的性能产生重大影响。

箭头表示多年来不同标准的演变。请注意,标准定义的高通滤波器(HPF)带宽会随着时间的推移而增加,而低通滤波器(LPF)带宽通常由 SerDes 供应商而非标准定义。一个重要的结论是,采用传统的 12 kHz 至 20 MHz 方法所产生的误差只会随着时间的推移而增加。

由于存在这些局限性,有必要转而采用更精确和针对特定应用的方法来评估 refclk 抖动。

过滤相位抖动的新方法

针对传统方法的不足,我们提出了一种更有意义的相位抖动滤波器方法。这种方法由PCI-SIG 电气工作组开发,包括使用相关应用的特定抖动滤波器,并考虑相位噪声混叠。

实施新方法包括

测量相位噪声: 使用Keysight E5052B或Rhode & Schwarz FSWP 等相位噪声分析仪测量 refclk 的相位噪声。避免使用频谱分析仪或示波器进行此测量,因为它们可能会引入大量仪器噪声。例如,频谱分析仪无法将振幅噪声与相位噪声区分开来,这会导致对抖动做出乐观或悲观的估计,具体取决于信号的压摆率和其他因素。

扩展相位噪声数据: 将测量到的相位噪声数据平延伸至时钟频率的三次谐波。这一步骤考虑了实际系统中当串行解调器的传输锁相环(PLL)中的相位检测器对 refclk 进行采样时出现的相位噪声混叠现象。

应用系统滤波器: 将系统的抖动传递函数(包括适当的滤波器滚降)应用于相位噪声数据,包括扩展区域。这样就能准确模拟系统观测到的相位噪声。

积分相位噪声:对偏移频率上的滤波相位噪声进行积分,得出相位抖动值。该积分应至少从滤波器角频率的一个数量级开始。使用SiTime Studio等免费软件可自动进行这一整合。

我们建议时钟和定时行业在数据表中指定相位抖动时,从传统的 12 kHz-20 MHz 砖墙滤波器过渡到更有意义的 4-16A 滤波器。这里的 4-16A 指的是 4 MHz RX 时钟数据恢复 (CDR) 带宽和 16 MHz TX PLL 带宽,两者都具有一阶滚降(-20 dB/dec),并在抖动计算中包含混叠(“A”)。在未指定应用的情况下,这种方法可对现代串行解串器应用的抖动性能进行保守估计。或者,在指定应用时,应始终应用适当的特定应用滤波器。

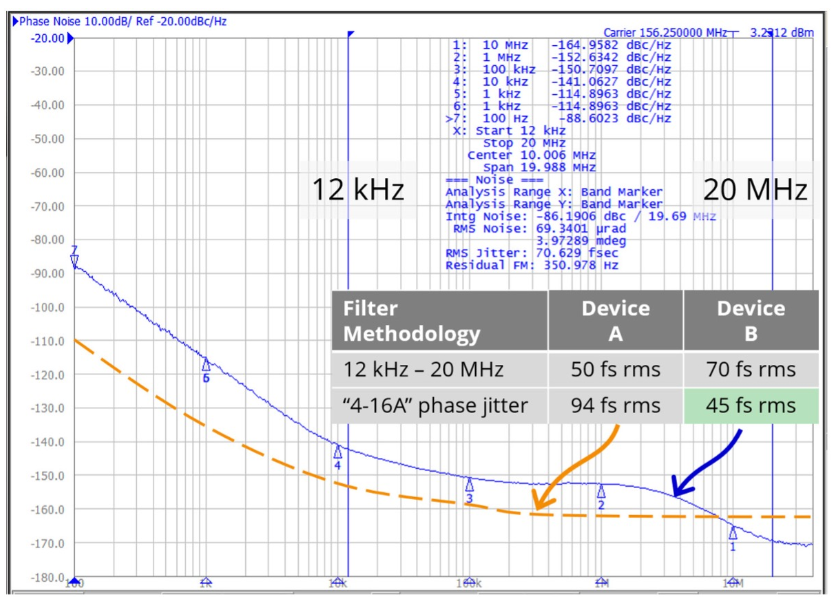

采用两种不同方法分析的两种产品得出了相反的结论。与传统方法相比,4-16A 相位抖动方法能更准确地预测高速串行链路的系统内性能。

按照上述步骤,与传统的 12 kHz 至 20 MHz 砖墙滤波器相比,4-16A 方法能更准确地反映高速 SerDes 应用中观察到的相位抖动。

为了说明新方法的有效性,让我们使用两个示例振荡器将其与传统方法进行比较:

设备 A:传统的 12 kHz 至 20 MHz 相位抖动: 50 fs rms -- 结论: 设备 A 最佳

设备 B 传统的 12 kHz 至 20 MHz 相位抖动: 70 fs rms

使用 4-16A 方法分析时:

设备 A:4-16A 相位抖动: 94 fs rms

设备 B:4-16A 相位抖动: 45 fs rms -- 结论: 设备 B 最佳

这个例子说明了新方法如何能对反向时钟源的性能得出不同的结论。在本例中,器件 B 在传统方法下似乎不太有利,但实际上在 4-16A 方法下表现更好,因为 4-16A 方法更准确地预测了终端应用观察到的抖动。

关于抖动的免费点播课程

Timing Essentials Learning Hub 专为在职专业人士设计,课程侧重于理论的实际应用,让您更深入地了解时序如何影响下一个设计的性能。

抖动基础

高速串行链路中的时钟抖动

PLL 如何过滤抖动

反射时钟抖动分析新方法的优势

在时钟和定时数据表中采用 4-16A 方法将带来几大好处:

优化系统性能: 通过使用能准确反映真实系统行为的方法,设计人员可以选择真正能提高系统性能的 Refclk 源。

降低复杂性: 清晰一致的反向时钟抖动规范简化了设计人员的选择过程,降低了选择次优元件的风险。

面向未来: 随着数据速率的不断提高,4-16A 方法变得更加重要,可为下一代系统提供精确的抖动测量。

用于分析 refclk 抖动的传统 12 kHz 至 20 MHz 砖墙滤波器方法虽然具有重要的历史意义,但已无法满足现代高速 SerDes 应用的需求。建议采用的 4-16A 相位抖动滤波器方法提供了一种实用、准确和针对特定应用的替代方法,符合当前的行业需求。

通过采用这种新方法,时钟和定时行业可以促进最佳链路性能和简化 refclk 选择。现在是业界采用一种反映高速数据通信实际情况的方法向前迈进的时候了,它将为持续创新和性能改进铺平道路。

- MEMS振荡器为何具有较高的耐久性和可靠性2024-07-19 15:01:537500

- 深入了解MEMS辅助温度传感器为何具有 20-µK 分辨率2024-07-18 10:39:036000

- SiTime具有 40 μK 分辨率的DualMEMS 谐振器时间数字转换器2024-07-17 11:21:013600

- 深入分析低带宽锁相环的高稳定性为何受控振荡器影响2024-07-16 18:02:337900

- ±0.01ppm高精度温补振荡器SiT5501如何改变边缘网络的精确计时市场2024-01-17 00:00:008870

- ±0.1ppm高精度温补振荡器SiT7910如何为航空航天和国防提供25倍精准计时2023-03-17 10:38:231433227

- 汽车级晶振选型设计指南2022-06-28 09:14:544700

- SiTime硅晶振在SSD存储中的应用2022-05-23 09:51:424400

- 示波器的两个最重要参数之示波器宽带和采样率详解2022-04-02 13:32:204000

- SiTime推出高性能XCalibur™有源谐振器SiT14082022-02-08 09:47:597922

- 汽车级晶振为自动驾驶ADAS保驾护航2021-08-20 13:39:175684

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483