SiT92110 评估板硬件用户手册~~用于评估 SiT92110

SiT92110 评估板硬件用户手册

1 、简介

SiT92110 评估板设计用于评估 SiT92110,这是一款 10 输出 LVCMOS 低抖动扇出缓冲器。

图 1 SiT92110 EVK 电路板

2 、特性

1) 加性抖动性能为 50 fs RMS。

2) 时钟输出之间的典型输出偏移为 30 ps。

3) 采用电平转换,核心电源电压为 3.3 V/2.5 V/1.8 V,LVCMOS 输出驱动器的输出电源电压为 3.3 V/2.5 V/1.8 V/1.5 V。

4) 设备输入包括初级、次级和晶体输入。

5) 通过对 SiT92110 的输入选择引脚进行编程来选择输入。SiT92110 的输入时钟接收器可接受 LVPECL、LVDS、LVCMOS、SSTL、HCSL 和 XTAL 波形。

6) 支持 8 MHz 至 50 MHz 的晶体频率。

7) 在晶体旁路模式下,晶体输入的过驱动频率可达 250 MHz。

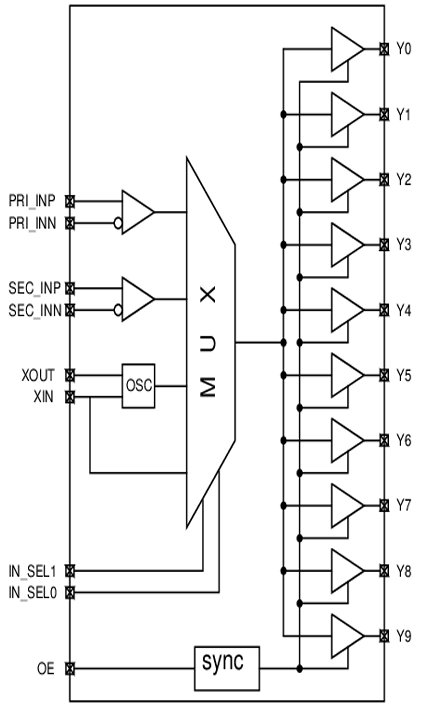

3 、功能说明

SiT92110 是一款 10 输出 LVCMOS 时钟扇出缓冲器,具有低附加抖动,工作频率高达 250MHz。它具有一个 3:1 输入多路复用器,带有一个可选晶体振荡器输入和 10 个 LVCMOS 输出。该器件采用 32 引脚 QFN 封装。

图 2 功能框图

3.1. VDD 和 VDDO 电源

SiT92110 具有独立的 3.3/2.5/1.8 V 内核 (VDD) 和 3.3/2.5/1.8/1.5 V 输出电源 (VDDO)。输出电源工作电压为 2.5/1.8/1.5 V,因此功耗更低,输出电平兼容 2.5/1.8/1.5 V 接收器设备。输出电平 LVCMOS (VOH) 参考其各自的 VDDO 电源。

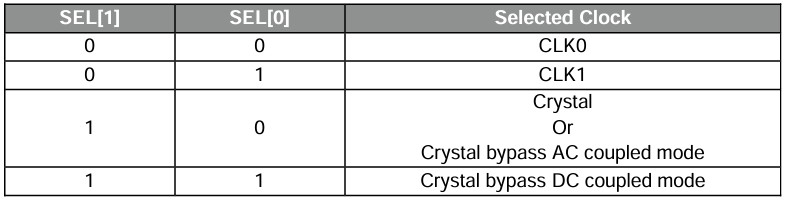

3.2. 时钟输入

输入时钟可从一级通用时钟输入、二级通用时钟输入或 Xin 中选择。时钟输入选择由 SEL[1:0] 输入控制,如表 1 所示。

表 1 输入时钟选择

3.3. 时钟状态(输入与输出状态)

表 2 输入与输出阶段

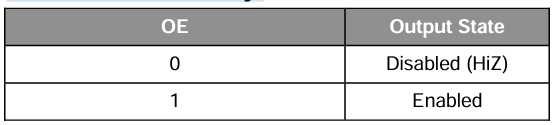

3.4. 输出启用

将 OE 拉至低电平,可在输入信号的下一个下降沿后强制输出进入高阻抗状态。只要 OE 为低电平,输出就保持高阻抗状态。OE 信号与所选输入时钟内部同步。这样就能在输入时钟下降沿以无间隙的方式禁用输出时钟。

表 3 OE 功能

4 、电源连接

SiT92110 缓冲器有两个电源 VDD 和 VDDO。VDDO 电源是输出 LVCMOS 驱动器的专用电源。VDDO 电源可以是 3.3V+/-5%、2.5V+/-5%、1.8V+/-10%、1.5V+/-10%。VDD 电源专用于 SiT92110 内部的输入时钟接收器、时钟分配单元和 XO。该电源独立于 VDDO。VDD 电源可在 3.3V+/-5%、2.5V+/-5% 和 1.8V +/- 5% 之间变化。VDD 和 VDDO 电源可根据表 4 进行设置。

表 4 SiT92110 EVK 的电源连接

将 USB 电缆从 PC/laptop USB 端口连接到 EVK 的 USB 接口。连接 USB 后,用户可以看到 LED D4 和 D5 发光。SiT92110 将使用板载 LDO 在 VDD=VDDO = 3.3V 电压下启动。通过表 5 中的跳线设置,可以将 LDO 编程为不同的电压电平。

表 5 设置 VDD 电源电压

注释

1. 跳线 J2 的连接请参阅示意图 1。

2. 在 EVK 的默认配置中,使用 U1 LDO 将 VDD 输出设置为 3.3V。

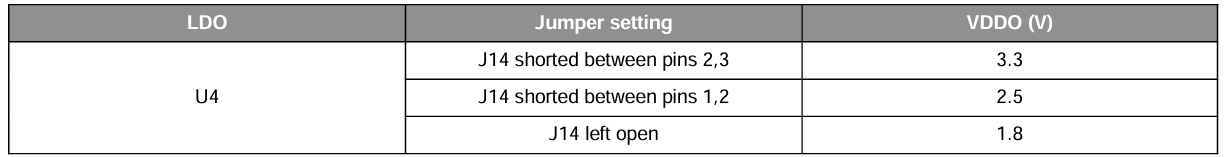

表 6 设置 VDDO 电压

注释

1. 跳线 J14 的连接请参阅示意图表 2。

2. 在 EVK 的默认配置中,使用 U4 LDO 将 VDDO 输出设置为 3.3V。

3. 选择 LDO 反馈电阻以支持 3.3、2.5 和 1.8V VDDO 工作。

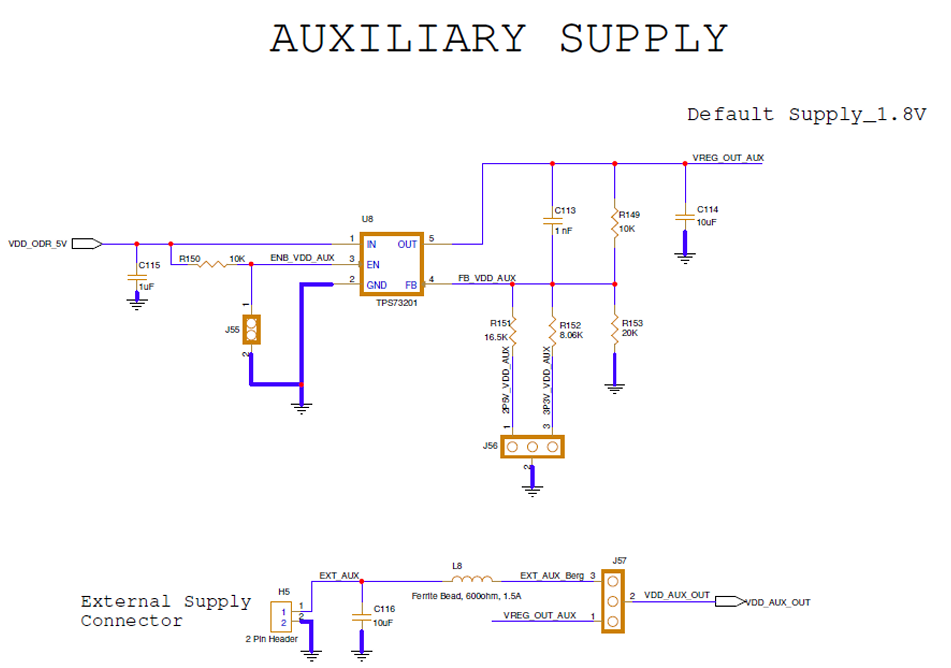

表 7 设置 VDD_AUX 电压

注释

1. 有关跳线 J56 的连接,请参阅示意图表 3。

2. VDD_AUX 是电平转换器输出的电源,用于自动控制输入时钟选择和输出使能。

3. 保持 VDD = VDD_AUX 4.

4. 在 EVK 的默认配置中,VDD_AUX 通过 U8 LDO 设置为 3.3 V。

5 、在 EVK 中设置输入时钟选择和输出使能

用于控制输入时钟选择和输出使能的跳线设置如下。

表 8 控制时钟选择和输出启用的跳线设置

注释

1. 输入时钟选择编程如下。输入时钟选择编程:2'b00 - clock0,2'b01 - clock1,2'b10 - XO

2. 有关跳线 J68、J67 的连接,请参阅示意图表 6。

3. OE 编程如下 OE 编程:1'b0 - 输出禁用,1'b1 - 输出启用

4. 4. 跳线 J70 的连接请参阅示意图表 6。

5. 5. J69 应始终保持默认状态:位于引脚 2 和引脚 3 之间。

6. 标有 JVDD1、JVDD2、JVDD3、Diag 的跳线应保持默认状态:浮动。

7. J8 应保持默认状态:位于引脚 1 和引脚 2 之间,以便为板载 LDO 供电。

6 、输入时钟配置

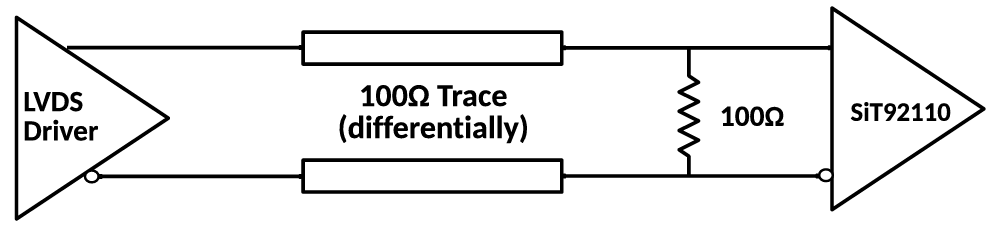

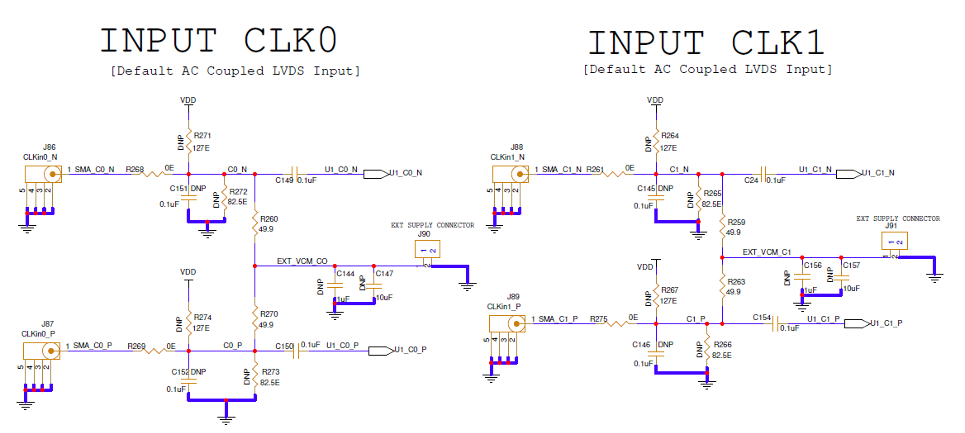

输入时钟采用交流耦合,并以差分 100 欧姆端接。因此,如原理图 7 所示,EVK 配置为差分输入时钟。

图 3 输入时钟配置

7 、配置单端交流耦合输入时钟

许多应用要求缓冲器接收单端输入时钟。因此,需要对 EVK 做一些最小的改动,以实现单端操作。

7.1. 使用 LVCMOS 驱动器驱动时钟输入(交流耦合)

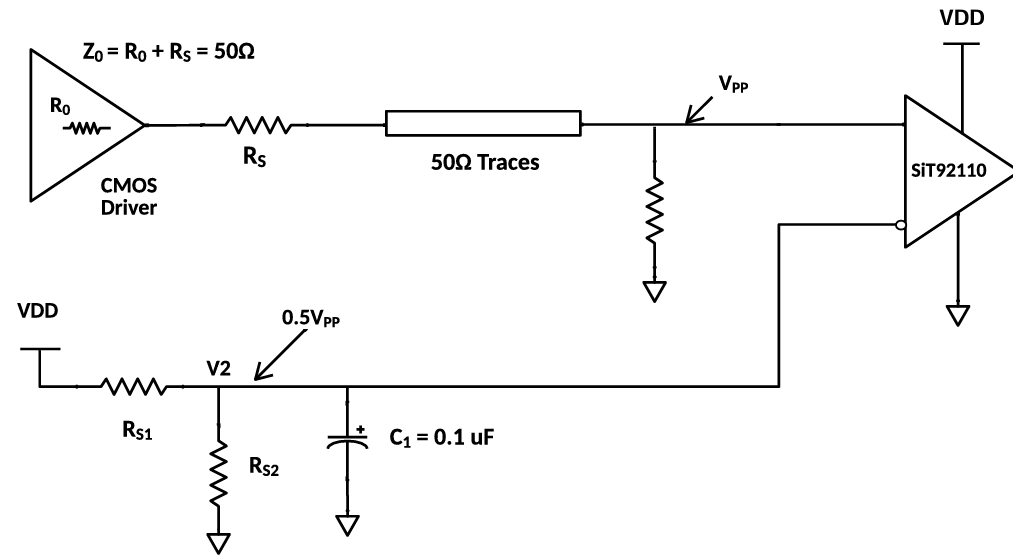

对于大型单端输入信号,如 3.3 V 或 2.5 V LVCMOS,应在输入端附近放置一个 50 Ω 负载电阻,用于信号衰减以防止输入过载,并用于线路终端以尽量减少反射。单端输入压摆率应尽可能高,以减少性能下降。时钟输入的内部偏置电压约为 (VDD-0.3)/2 V,因此输入可采用交流耦合,如图 4 所示。LVCMOS 驱动器加上 Rs 的输出阻抗应接近 50 Ω,以匹配传输线和负载终端的特性阻抗。

图 4 单端 LVCMOS 输入,交流耦合

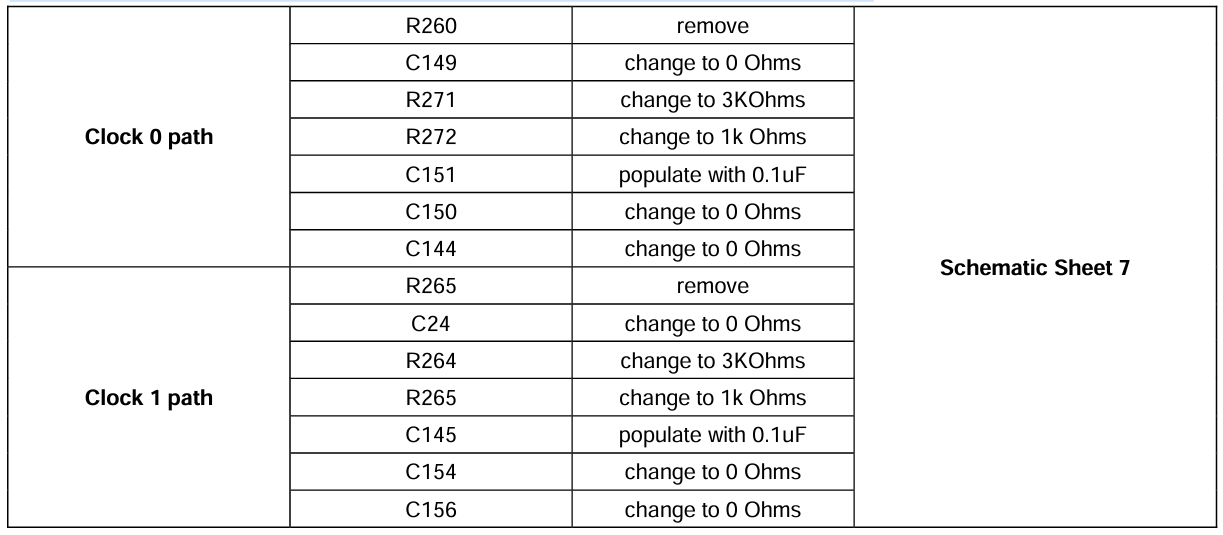

使用 LVCMOS 驱动器驱动时钟输入的 EVK 更改(交流耦合,单端)。表 9 列出了电路板的更改

表 9 支持单端交流耦合 LVCMOS 所需的电路板组件变更

8 、为直流耦合输入 LVCMOS 时钟配置 EVK

8.1. 使用 LVCMOS 驱动器驱动时钟输入(直流耦合)

单端时钟可以直流耦合到 SiT92110 缓冲器。如果驱动 CLK0,则必须使用电阻分压器设置 nCLK0 电压,以匹配直流耦合单端时钟的共模。如图 5 所示。

图 5 直流耦合单端 CMOS 输入时钟

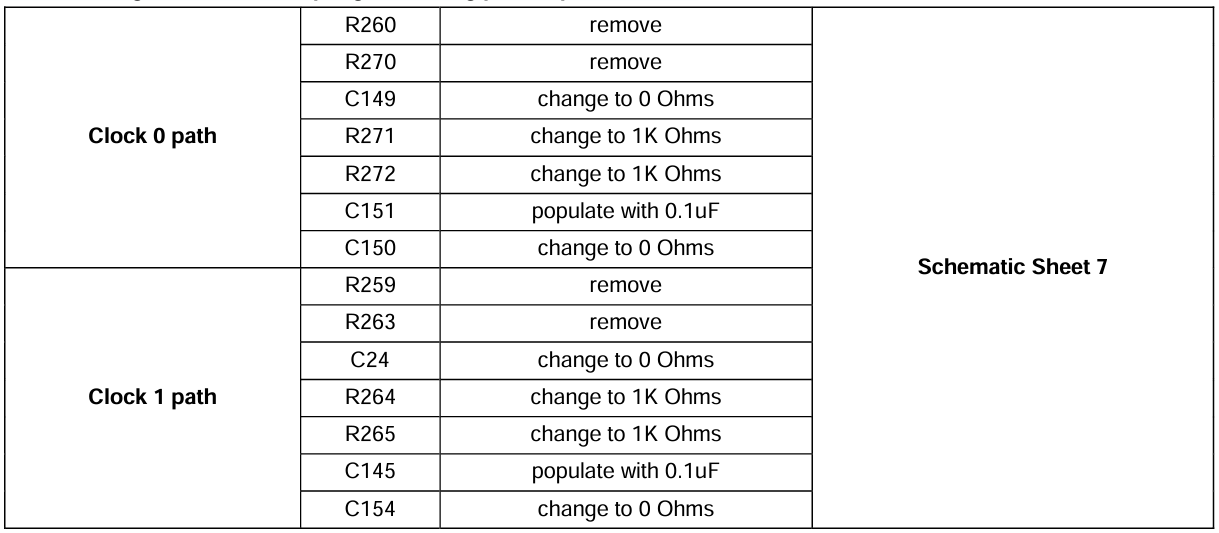

8.2. 使用 LVCMOS 驱动器驱动时钟输入时的 EVK 变化(直流耦合、单端)

案例 1: 让我们来看看一个 LVCMOS 驱动器(阻抗为 50 欧姆)驱动位于 SiT92110 输入端的 50 欧姆负载的情况。假设 LVCMOS 驱动器的电源电压为 1.8 V,则芯片输入端的时钟摆幅为 0.9 Vpp。我们将基准节点的基准电压设置为 0.45 V。选择 VDD = 1.8 V,Rs2=3Rs1,Rs1、Rs2 应在千欧范围内。因此,如果我们设置 Rs1=3K, Rs2=1K。

表 10 支持单端直流耦合 LVCMOS 所需的 EVK 电路板更改

情况 2:如果负载是纯电容性的,那么我们只需在参考节点上安装 0.1uF 的电容器,使其浮动。参考节点内部偏置为 VDD/2。

图 6 单端 LVCMOS 输入,直流耦合 电容性负载

表 11 驱动纯电容性负载的单端直流耦合

9 、驱动差分 LVDS 或 LVDS 升压(交流耦合)

输入端有一个 100 欧姆的差分电阻,为 LVDS 或 LVDS 升压提供电流通路。100 欧姆差分信号由 0.1uF 的交流耦合电容跟随。因此,无需改变电路板配置。

图 7 LVDS 或 LVDS 升压交流耦合

10 、驱动直流耦合 LVDS 的电路板配置

10.1. LVDS (直流耦合)

使用尽可能靠近接收器的 100 欧姆差分端子。如图 8 所示。

图 8 直流耦合 LVDS 的端接方案

表 12 直流耦合 LVDS 或 LVDS 升压所需的电路板更改

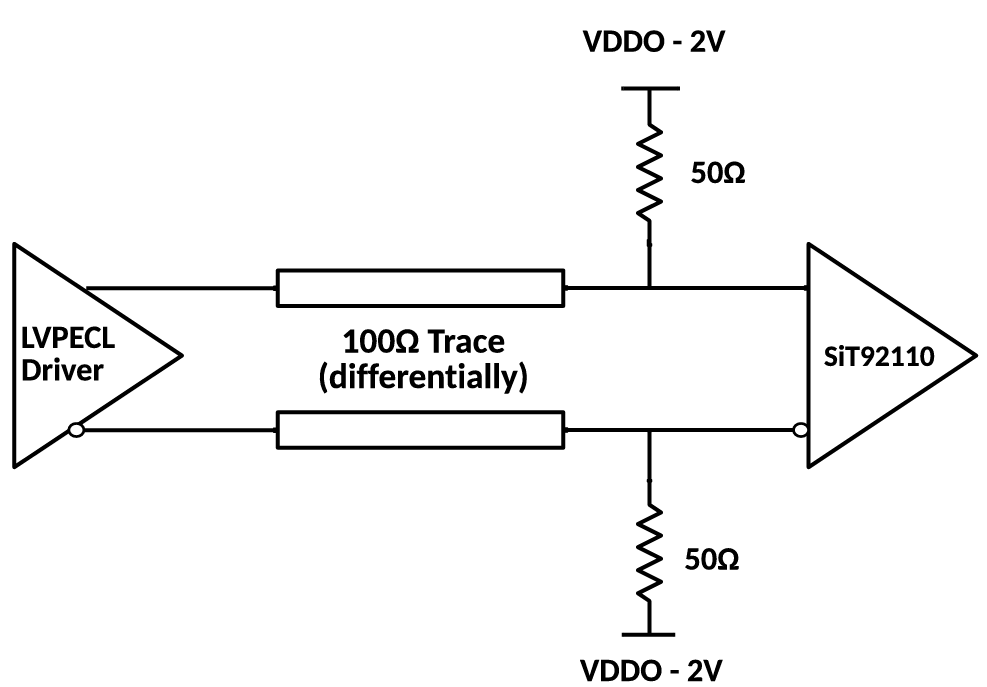

11 、驱动 DC/AC 耦合 LVPECL 所需的电路板配置

11.1. 直流/交流耦合 LVPECL

LVPECL 标准要求输入时钟驱动器采用直流路径。接收器上的 50 欧姆端接采用 VDDO-2V 偏置。VCM(VDD-2V)需要能够吸收或输出电流。可通过跳线 J90、J91 在输入时钟电路中提供 VCM。

因此,无需更改电路板,只需通过跳线 J90、J91 给 VCM 供电即可。

图 9 直流耦合 LVPECL 的端接方案

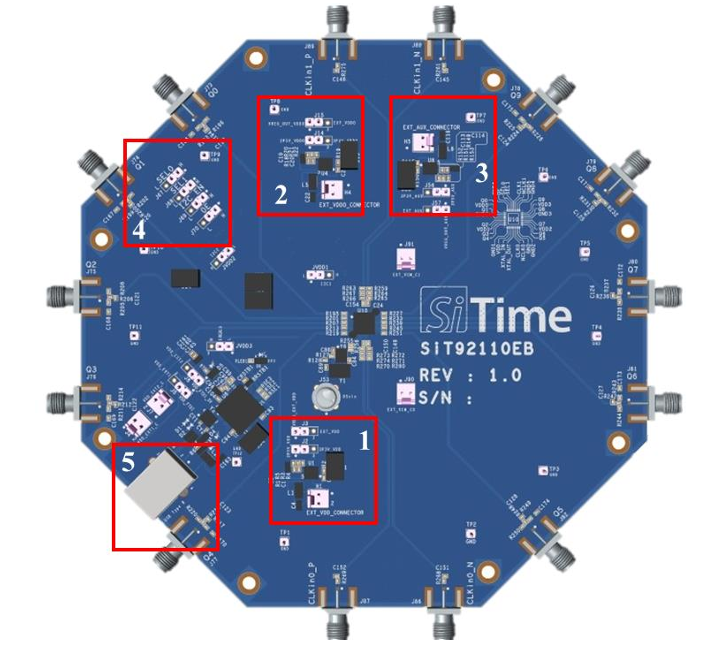

12 、EVB 快照

图 10 EVB 简图

区块 1 具有跳线设置,用于配置表 5 所述的芯片 VDD。

区块 2 的跳线设置用于配置芯片 VDDO,如表 6 所示。

区块 3 的跳线设置用于配置芯片 VDD_AUX,如表 7 所示。

区块 4 有跳线可以选择时钟输入(SEL0 和 SEL1),并设置输出使能(OE),如表8中提到的。区块 5 有 USB 端口,可以用来给板子供电,或者选择使用外部电源供电,如表4中提到的。

13 、电路板原理图

13.1. 原理图1

图 11 原理图 1 - VDD 输入侧电源

13.2. 原理图 2

图 12 原理图 2 - VDDO 输出端电源

13.3. 原理图 3

图 13 原理图 3 - 辅助电源

13.4. 示意图 4

图 14 原理图 4 - USB 连接

13.5. 原理图5

图 15 原理图 5 - FTDI 连接

13.6. 原理图 6

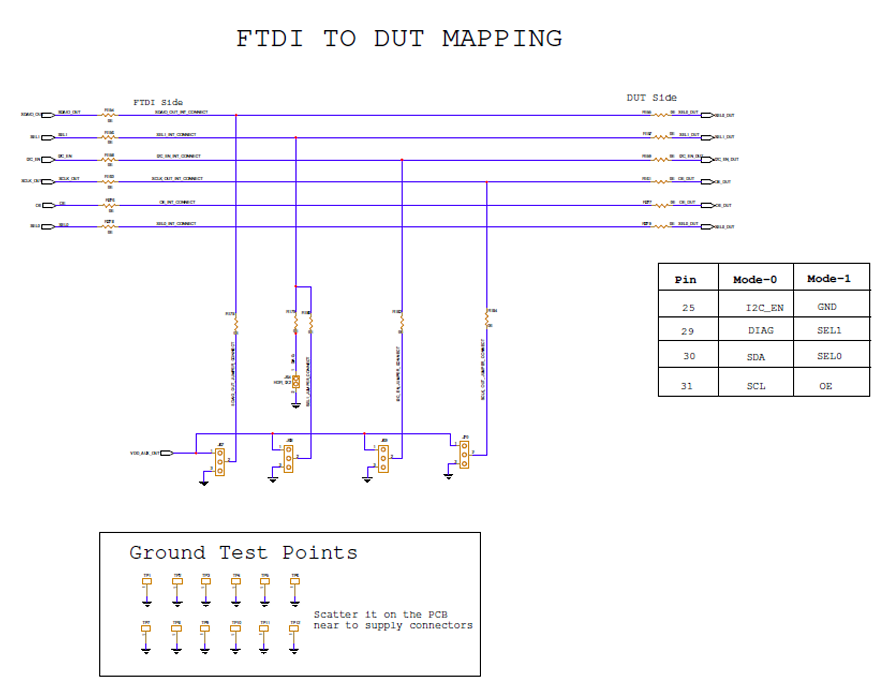

图 16 原理图 6 - FTDI 到 DUT 映射

13.7. 原理图 7

图 17 原理图 7 - 输入时钟

13.8. 原理图8

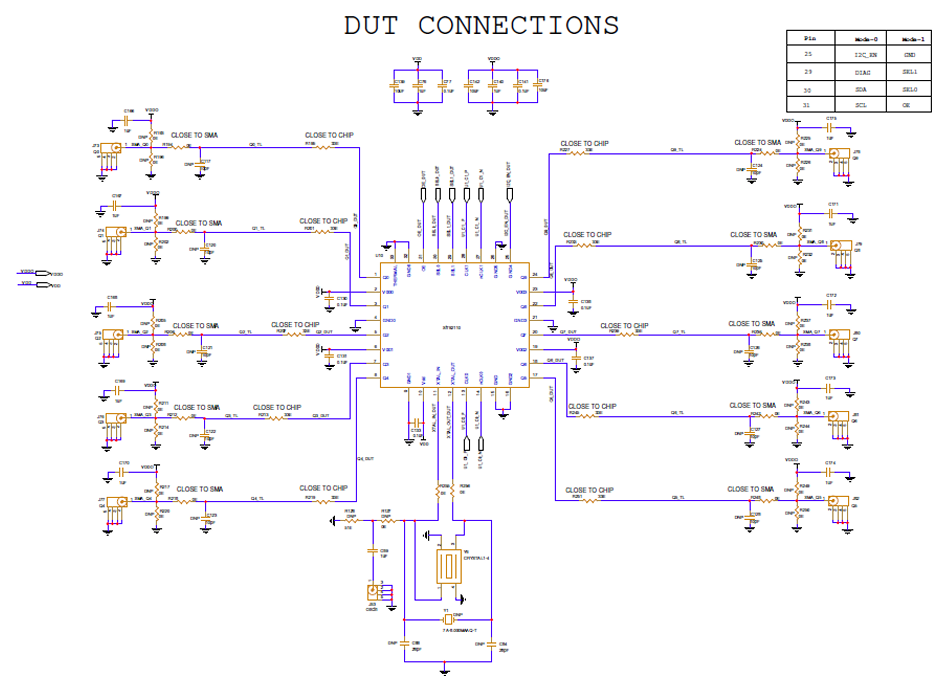

图 18 原理图 8 - DUT 连接

- MEMS振荡器为何具有较高的耐久性和可靠性2024-07-19 15:01:537500

- 深入了解MEMS辅助温度传感器为何具有 20-µK 分辨率2024-07-18 10:39:036000

- SiTime具有 40 μK 分辨率的DualMEMS 谐振器时间数字转换器2024-07-17 11:21:013600

- 深入分析低带宽锁相环的高稳定性为何受控振荡器影响2024-07-16 18:02:338500

- ±0.01ppm高精度温补振荡器SiT5501如何改变边缘网络的精确计时市场2024-01-17 00:00:008870

- ±0.1ppm高精度温补振荡器SiT7910如何为航空航天和国防提供25倍精准计时2023-03-17 10:38:231433227

- 汽车级晶振选型设计指南2022-06-28 09:14:544800

- SiTime硅晶振在SSD存储中的应用2022-05-23 09:51:424400

- 示波器的两个最重要参数之示波器宽带和采样率详解2022-04-02 13:32:204000

- SiTime推出高性能XCalibur™有源谐振器SiT14082022-02-08 09:47:597922

- 汽车级晶振为自动驾驶ADAS保驾护航2021-08-20 13:39:175784

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483