SiT6712EB 评估板 支持 5.0x3.2 mm 10 引脚 QFN 封装的差分信号输出

SiT6712EB 评估板用户手册

1 、简介

SiT6712EB 评估板 (EVB) 设计用于 SiTime 的系统内可编程振荡器 (ISP-DCXO),支持 5.0x3.2 mm 10 引脚 QFN 封装的差分信号输出。它使用户能够评估 ISP-DCXO 器件的各个方面,包括信号完整性、相位噪声、相位抖动以及通过 I²C/SPI 接口重新编程输出频率。

EVB 功能

1,支持 SiT3521(1 至 340 MHz)和 SiT3522(340.000001 至 725 MHz)ISP-DCXO

2,用于测量输出频率的探测点

o 支持 LVPECL、LVDS 和 HCSL 输出信号类型

o 支持波形测量

o 支持相位噪声和相位抖动测量

3,连接 I²C 和/或 SPI 接口的连接器

4,用于测量电流消耗的连接器

SiTime 通常根据用户指定的 ISP-DCXO 设备预配置 EVB。最终用户可以为不同配置的 ISP-DCXO 器件重新配置 EVB。

有关 EVB 配置和使用的详情,请参阅第 3 节。

2、 输入/输出说明

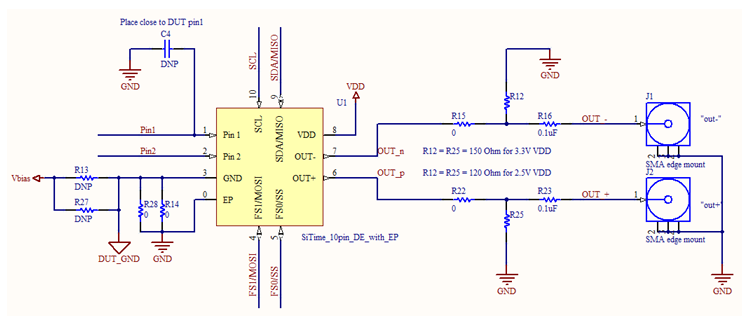

表 1 介绍了电路板的输入/输出连接器。

表 1:SiT6712EB 输入/输出

注:EVB 上 ISP-DCXO 器件的引脚 1 位置由器件基底周围丝印图案的倒角表示。

3 、EVB 使用说明

3.1 EVB 配置

SiT6712EB 通过使用不同的元件加载选项,支持 SiTime 差分振荡器不同信号类型的多种配置。

请参考

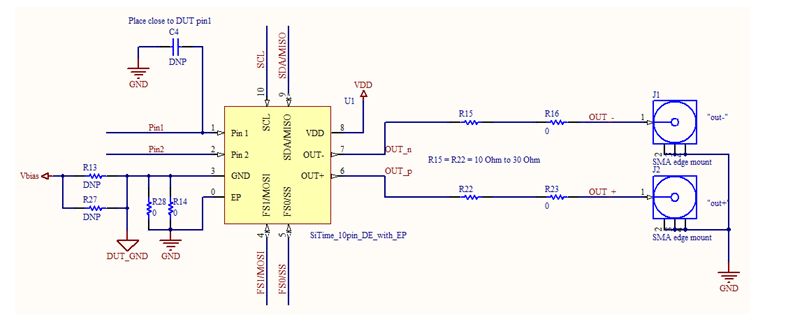

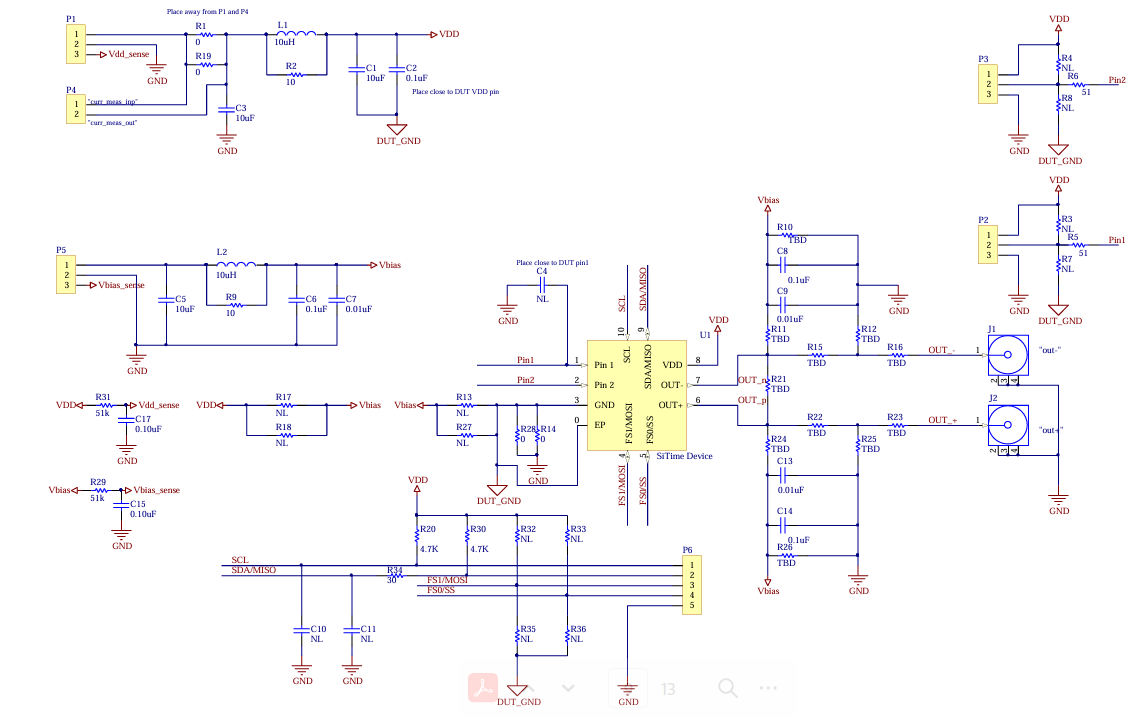

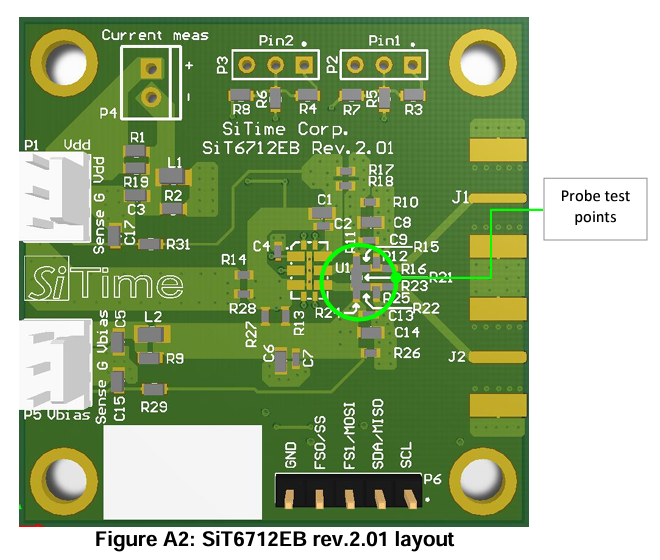

- 附录 A 图 A1 中的 SiT6712EB 原理图

- 附录 A 图 A2 为 SiT6712EB 布局俯视图

请注意,并非所有 EVB 配置都会使用示意图中显示的所有组件。具体来说、

- 任何具有指定标称值的组件均用于 EVB 的所有配置中

- 任何没有指定标称值的组件仅在 EVB 的特定配置中填充,因为这些配置需要这些组件。

- 任何标有 “DNP ”的部件均未在 EVB 上填充,仅供 SiTime 内部使用。

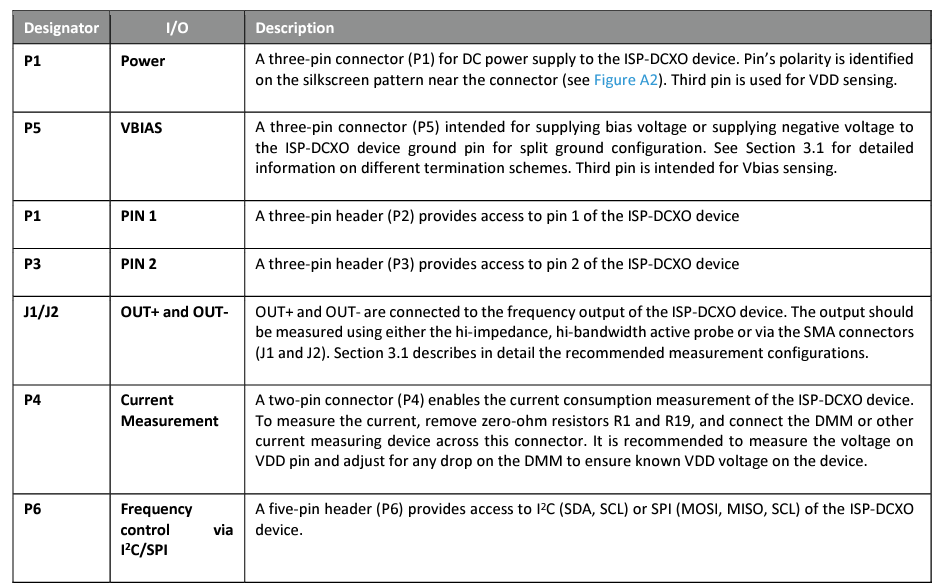

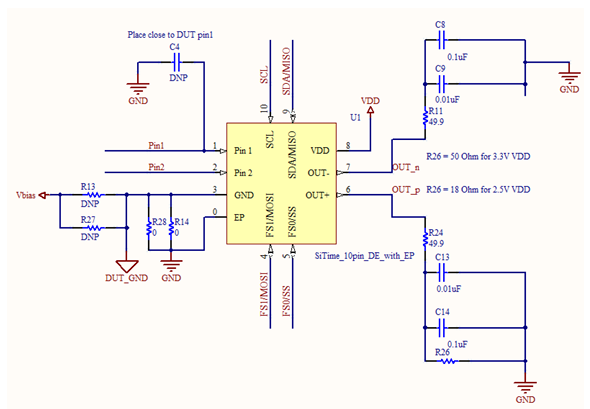

3.1.1 LVPECL,标准端接,有源探头 在此配置中,LVPECL 输出端接至 Vbias = VDD - 2 V,使用 50 Ω 电阻器 (R11 和 R24)。高速有源探头(如图 1 所示)放置在端接电阻器的焊盘上,该焊盘位于 OUT+ 和 OUT- 两条线路上。图 1 显示了这种配置的端接方案。

图 1:50 Ω 至 Vbias 的 LVPECL 输出端接,使用高阻抗和高带宽有源探头进行测量

3.1.2 LVPECL,交流耦合配置,直接连接仪器

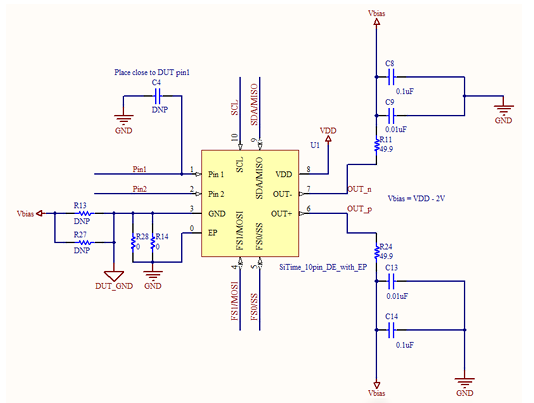

这是带 LVPECL 器件的评估板的默认装运配置。

此配置允许使用 50 Ω 同轴电缆将 LVPECL 输出连接到测量仪器。输出端通过 150 Ω/120 Ω(R15 和 R22;分别用于 3.3 V 和 2.5 V VDD)端接至 DUT 侧的 GND,并通过 0.1 uF 串联电容器(R16 和 R23)连接至 SMA 连接器。图 2 显示了这种配置的端接方案。

图 2:LVPECL 输出端接,150 Ω/120 Ω 至 GND,使用 50 Ω SMA 电缆与测量仪器进行交流耦合连接测量

3.1.3 LVPECL,Y 型端接,有源探头

此配置用于使用有源探头测量 LVPECL 输出波形参数。

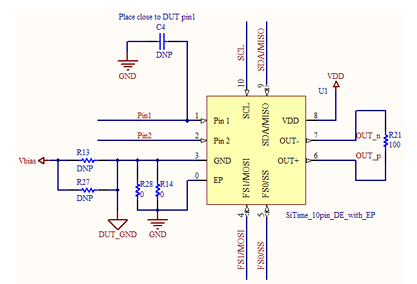

图 3 显示了该配置的端接方案。R26 与 R24(50 Ω)和 R11(50 Ω)一起为 OUT+ 和 OUT- 建立直流电压偏置。对于 3.3 V VDD,R26 为 50 Ω;对于 2.5 V VDD,R26 为 18 Ω。

图 3:LVPECL 输出端接的 Y 端接方案,用于使用高阻抗和高带宽有源探头进行测量

3.1.4 LVDS,标准终端,有源探头

此配置用于使用有源探针测量 LVDS 输出波形参数。高速有源探头(如图 4 所示)置于 OUT+ 和 OUT- 轨道上的终端电阻焊盘上。

图 4, 显示 OUT+ 和 OUT- 两端的差分阻抗为 100 Ω (R21),用于端接。

图 4:使用高阻抗和高带宽有源探头测量 LVDS 输出端的 100 Ω 差分阻抗

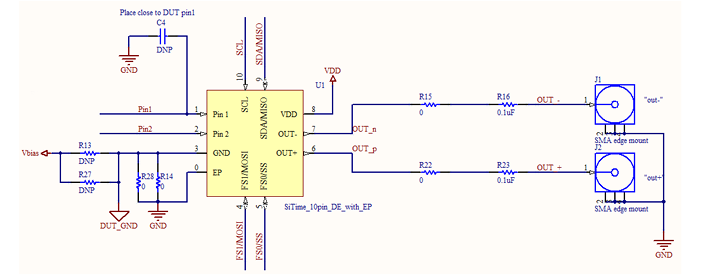

3.1.5 LVDS,交流耦合配置,直接连接仪器

这是带 LVDS 设备的评估板的默认出货配置。

该配置适用于将 LVDS 输出连接到测量仪器的 50 Ω 输入通道。交流耦合电容器(R16 和 R23)可阻断 LVDS 输出端的直流共模电压,避免 50 Ω 输入端产生直流电流。图 5 显示了这种配置的端接方案。

图 5:交流耦合 LVDS 输出端由测量仪器输入的 50 Ω 阻抗终止,OUT+ 和 OUT- 之间的等效阻抗为 100 Ω。

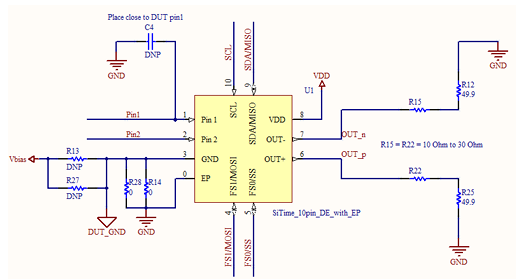

3.1.6 HCSL,标准端接,有源探头

此配置用于使用有源探头测量 HCSL 输出波形参数。输出端接 50 Ω(R12 和 R25)至 GND。串联电阻 R15 和 R22 用作过冲限制器,范围应在 10 Ω 至 30 Ω 之间。高速有源探头放置在终端电阻器的焊盘上,该焊盘位于 OUT+ 和 OUT- 两条线路上。图 6 显示了这种配置的终端方案。

图 6:通过 10 Ω 至 30 Ω 串联电阻器将 50 Ω 端接至 GND 的 HCSL 输出端接,以便使用高阻抗和高带宽有源探头进行测量

3.1.7 HCSL,标准终端,直接连接仪器

这是带 HCSL 设备的评估板的默认装运配置。

此配置用于测量 HCSL 输出波形参数,可直接连接到测量仪器的 50 Ω 输入端。图 7 显示了此配置的端接方案。串联电阻 R15 和 R22 用作过冲制器,范围应在 10 Ω 至 30 Ω 之间。

图 7:HCSL 输出端在测量仪器侧用 50 Ω 至 GND 端接,在源侧用 10 Ω 至 30 Ω 串联电阻器端接

3.2 I2C 和 SPI 接口

通过 P6 5 针连接器支持 I2C 和 SPI 接口。要支持 I2C,必须安装两个上拉电阻器 R20(4.7 kΩ)和 R30(4.7 kΩ)。SPI 接口不需要这两个电阻。EVB 出厂时已根据用户要求预配置为支持 I2C 或 SPI。

3.3 使用有源探头测量波形

SiTime 建议使用以下设备来正确测量差分时钟波形:

1) 带宽大于 4GHz 的差分有源探头,负载电容小于 1pF,如 Agilent 1134A,带高速差分探头,如:

a. Agilent E2675B 差分浏览器

b. Agilent N5381B 焊接探头端头

c. Agilent N5425B/N5426A ZIF 探头端头

2) 带宽为 4 GHz 或更高的示波器

3) 50 Ω 输入的示波器。

请参阅图 8,了解使用有源探针对 EVB 进行探测的示例。

图 8:SiT6712EB EVB 上用于捕捉波形的测试点上的差分浏览器(高阻抗有源探头)

3.4 抖动测量

对于抖动测量,应使用 3.1.1 (LVPECL)、3.1.4 (LVDS) 和 3.1.6 (HCSL) 中描述的配置。SiTime 应用说明 AN10007 中介绍了抖动测量技术。

附录 A - SiT6712EB 的示意图、BOM 和布局

图 A1:SiT6712EB rev. 2.01 原理图

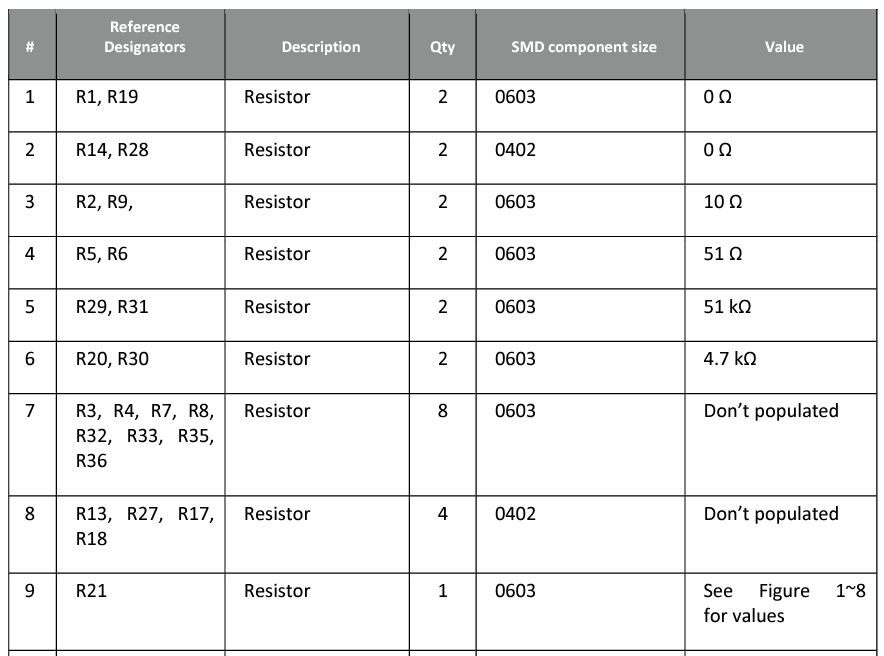

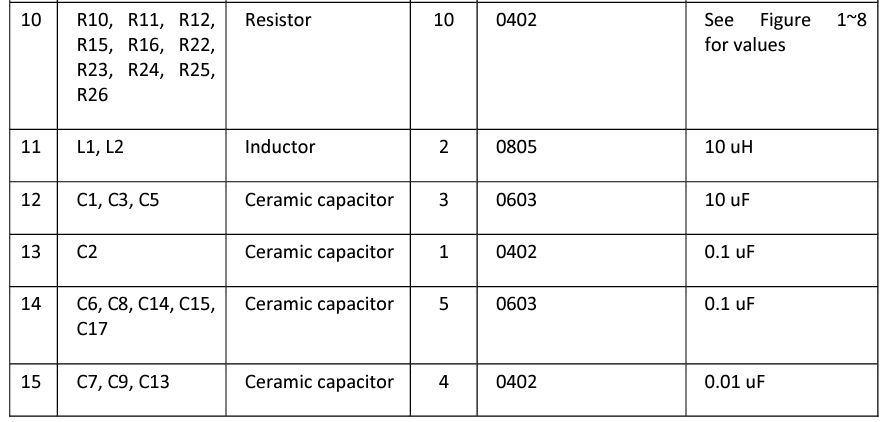

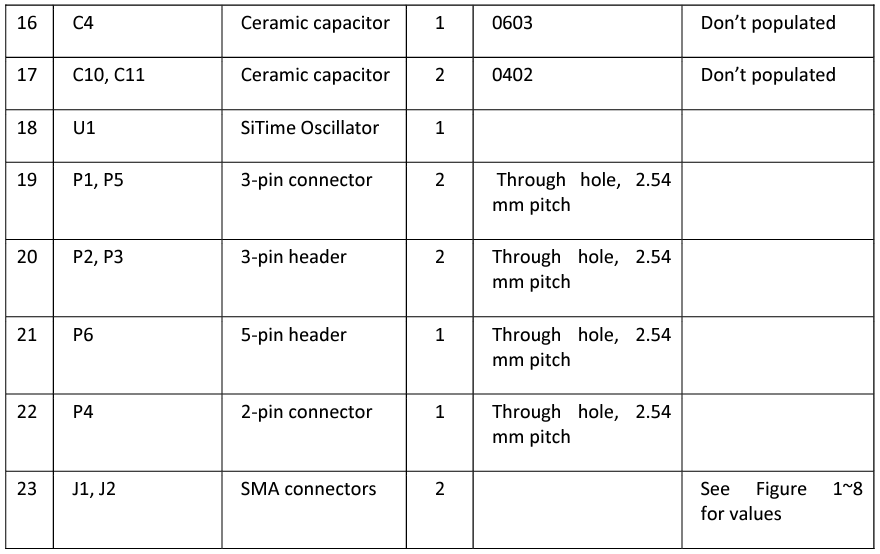

表 A1:物料清单(BOM)

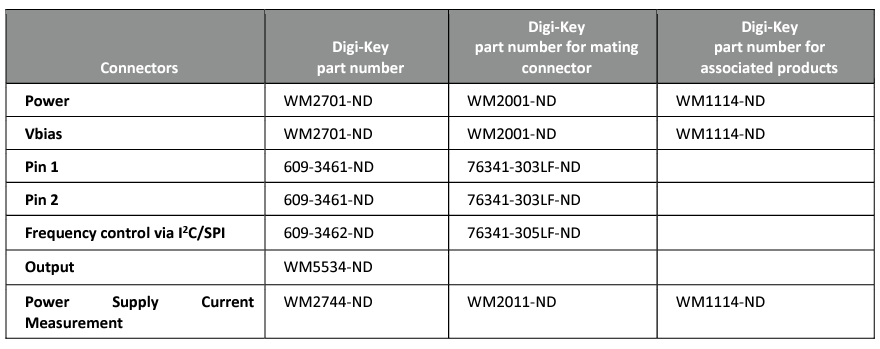

表 A2:连接器 Digi-Key 零件编号

- MEMS振荡器为何具有较高的耐久性和可靠性2024-07-19 15:01:537500

- 深入了解MEMS辅助温度传感器为何具有 20-µK 分辨率2024-07-18 10:39:036000

- SiTime具有 40 μK 分辨率的DualMEMS 谐振器时间数字转换器2024-07-17 11:21:013600

- 深入分析低带宽锁相环的高稳定性为何受控振荡器影响2024-07-16 18:02:338500

- ±0.01ppm高精度温补振荡器SiT5501如何改变边缘网络的精确计时市场2024-01-17 00:00:008870

- ±0.1ppm高精度温补振荡器SiT7910如何为航空航天和国防提供25倍精准计时2023-03-17 10:38:231433227

- 汽车级晶振选型设计指南2022-06-28 09:14:544800

- SiTime硅晶振在SSD存储中的应用2022-05-23 09:51:424400

- 示波器的两个最重要参数之示波器宽带和采样率详解2022-04-02 13:32:204000

- SiTime推出高性能XCalibur™有源谐振器SiT14082022-02-08 09:47:597922

- 汽车级晶振为自动驾驶ADAS保驾护航2021-08-20 13:39:175784

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483