低抖动汽车级差分晶振SiT9396如何应用PCI Express

引言

现代车辆对自动驾驶(AD)和高级驾驶辅助系统(ADAS)功能不断增长的需求,推动了汽车电子系统数量和复杂性的增加。这些系统配备了众多传感器,会生成大量数据,并需要更高的计算能力。由于单个 SoC 可能不足以满足计算需求,因此经常使用协处理器。PCI Express®(PCIe)是用于连接这些组件的常用接口之一。

诸如 AD/ADAS 等汽车应用需要超低延迟的实时处理。需要可靠且强大的定时解决方案来支持通过 PCIe 在处理器之间进行数据传输。本文将讨论 PCIe 时钟的关键考虑因素,包括时钟树架构、抖动、信号类型、EMI 降低和稳定性。

汽车中的 PCIe

PCI Express 是 2003 年创建的点对点串行接口,最初用于计算行业。它针对封闭的高度集成系统进行了优化,例如当今车辆中的 AD/ADAS、域控制器或区域控制器。PCIe 标准已成为汽车首选的高速接口之一,并拥有强大且成熟的生态系统。

PCIe 是一种双向总线,基于一对单向通道(每个方向各一个)。最多可以并行聚合 16 个通道以提高传输速率。PCIe 的带宽每一代都翻倍。每通道的传输速率从 PCIe Gen 1 中的 2.5 GT/S(G 传输/秒)和每通道 250MB/秒,发展到 PCIe Gen 6 中的 64 GT/s 和 7.56GB/秒。PCIe Gen 4 目前在汽车系统中被广泛使用。Gen 4 具有 16 GT/s,每通道速率为 1.97GB/秒。

PCIe 时钟

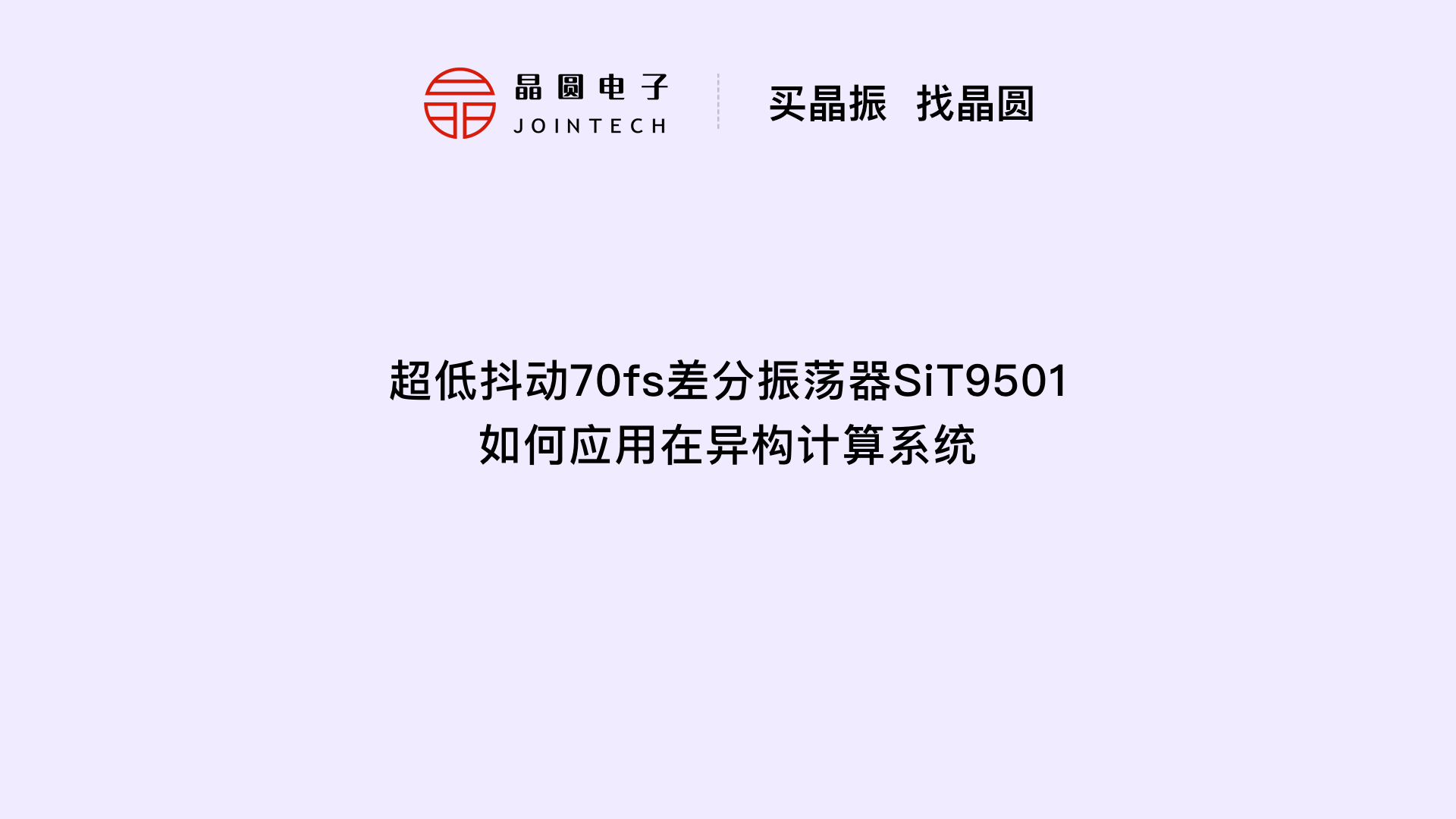

图 1 展示了一个具有一个 PCIe 接口的汽车 ECU(电子控制单元)示例。PCIe 接口在总线的每一端都需要一个 100 MHz 的时钟。在这个框图中,建议使用多个 SiTime MEMS 振荡器,包括在 PCIe 总线的每一端使用超低抖动的 SiT9396 振荡器。

图 1:具有一个 PCIe 接口的汽车 ECU(电子控制单元)的框图

下面列出了 PCIe 时钟中需要考虑的几个参数。每个参数将在以下部分进行讨论。

• 抖动,取决于 PCIe 世代

• 信号类型:HCSL 或 LP-HCSL

• 频率精度和稳定性

• 用于降低 EMI 的扩频

• 时钟树架构:公共时钟或独立参考

抖动时钟

抖动是对任何高速串行接口进行时钟控制时需要考虑的一个重要因素。抖动被定义为假定为周期性信号的真实周期性的偏差。[1] 换句话说,抖动会导致时钟信号(其具有周期性)的上升沿和下降沿过早或过晚上升或下降。抖动有很多原因,例如热噪声、串扰或者仅仅是性能不佳的时钟源。过度的抖动会使 PCIe 链路的眼图闭合,从而导致总线上的传输错误。

随着每一代 PCIe 数据速率的增加,如表 1 所示,需要更低的抖动。必须选择抖动水平低于每一代 PCIe 允许限值的时钟源。

表 1:每一代 PCIe 常见时钟架构的抖动限值

SiTime 兼容 PCIe 的时钟源,例如 汽车级差分晶振SiT9396,支持 PCIe Gen 1 到 Gen 6。

信号类型:HCSL 和 LP-HCSL

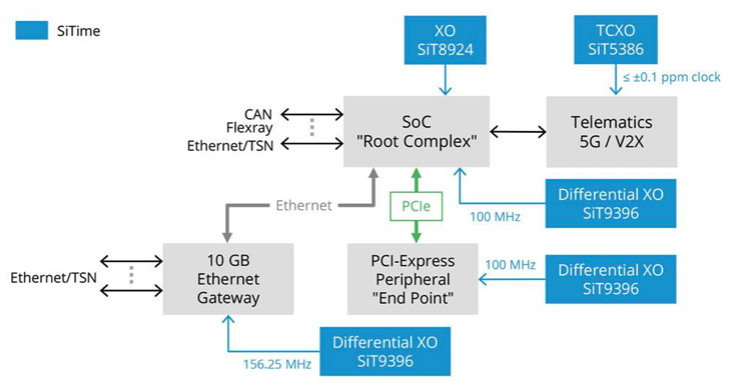

由 PCI-SIG 开发的 PCI Express 标准最初指定了 HCSL 信号。HCSL 输出由电流发生器驱动,这需要一个 4 电阻终端在目标级创建所需的电压。

现代系统使用 LP-HCSL(低功耗 HCSL)。输出是电压驱动的,因此不再需要终端。除了节省功率外,HP-HCSL 每通道和时钟节省 2 个电阻,减少了电路板空间和物料清单成本。此外,当总线停止时,LP-HCSL 输出可以完全关闭,使功率降至几乎 0 毫安。相比之下,无论总线是活动还是停止,HCSL 都会持续消耗电流。

HCSL 需要外部电阻:串联电阻 RS = 33 Ω 终端电阻 RT = 50 Ω LP-HCSL

HCSL 需要外部电阻:串联电阻 RS = 33 Ω 终端电阻 RT = 50 Ω LP-HCSL

不需要终端电阻。此外,串联电阻 RS = 33 Ω 通常集成在芯片上(底部)。SiTime 器件具有片上内部电阻。

不需要终端电阻。此外,串联电阻 RS = 33 Ω 通常集成在芯片上(底部)。SiTime 器件具有片上内部电阻。

图 2:HCSL、LP-HCSL 和集成电阻的 LP-HSCL 输出

频率精度和稳定性

时钟的频率精度以百万分之一(ppm)或十亿分之一(ppb)表示,可分为两部分:

• 初始精度:在 25°C 时与目标频率的偏差。不考虑温度影响和老化。

• 全温度范围内的稳定性:在整个工作温度范围内与目标频率的偏差。

时钟的总精度包括初始精度、全温度范围内的稳定性以及其他可能影响精度的因素,如老化。

PCIe Gen 1 至 4 要求总精度为±300 ppm。PCIe Gen 5 及以上要求±100 ppm。在本文档的其余部分,我们将在示例中使用 PCIe Gen 1 至 Gen 4 的±300 ppm 要求。

扩频以降低电磁干扰 PCI-SIG 标准预见到了扩频时钟(SSC)的使用。SSC 的目的是减少电磁辐射以符合 EMC(电磁兼容性)标准。SSC 以以下参数调制 100MHz 的 PCIe 时钟频率。

• 允许的调制频率范围(根据 PCI-SIG 规范)为 30kHz 至 33kHz [2]

• 向下扩展,这意味着调制频率始终低于 100MHz 的载波频率,这与围绕载波频率对称调制的中心扩展不同

• 最大调制幅度为 0.5%

图 3:由分辨率带宽为 100kHz 的频谱分析仪测量的非扩展时钟和扩频时钟 [3]

PCIe 时钟树架构

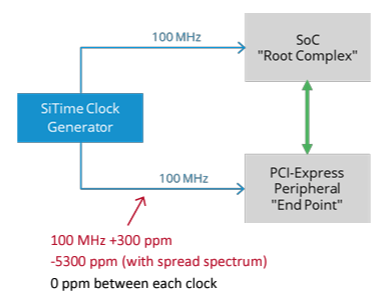

公共时钟架构 公共时钟架构可能是最简单的 PCIe 时钟架构,也是迄今为止使用最频繁的架构。在这种架构中,根联合体以及每个端点(可能不止一个)都从同一个时钟发生器接收其时钟信号。简单来说,时钟发生器就像一个具有多个输出的振荡器。

由于所有时钟信号都来自同一源,因此每个时钟上的扩频调制彼此同相。其频率因此为:

• 100 MHz ±300 ppm(扩频时钟(SSC)未激活)

• 100 MHz +300 ppm 至 -5300 ppm(SSC 激活,最大可能调制)

• 所有时钟之间的频率差为 0 ppm

公共时钟架构简单而优雅。一个设备为整个 PCIe 系统提供时钟;SSC 可以随意激活;并且电路板空间被缩减到最小。

图 4:公共时钟架构

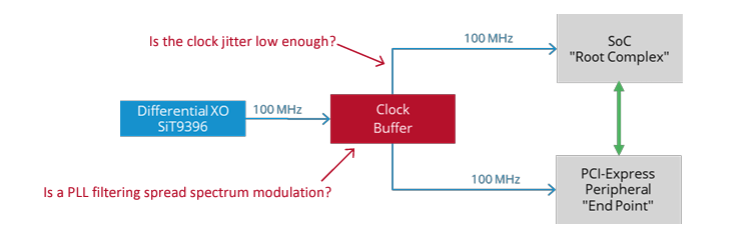

振荡器 + 缓冲器(效果良好,但并非最佳架构)

PCIe 时钟缓冲器存在的原因是将来自主板的输入时钟分配到计算机或服务器中的附加卡或夹层卡。由于汽车系统通常在一个 PCB 板内使用 PCIe,因此很少(如果有的话)需要分配外部时钟。

然而,PCIe 公共时钟架构的常见实现包括一个振荡器,后面跟着一个时钟缓冲器。有几个要点需要考虑:

• 需要两个组件而不是一个,增加了物料清单(BOM)。

• 时钟缓冲器会增加抖动。必须注意缓冲器输出端的抖动满足上述提到的抖动要求。不过,在实际中,这很少成为问题。

• 一些 PCIe 时钟缓冲器具有内部 PLL,其目的是衰减输入时钟的抖动。此功能是出于分配外部时钟的用例考虑,外部时钟的抖动可能在长走线或电缆上恶化。基于 PLL 的时钟缓冲器不会通过任何扩频调制。如果需要扩频,请务必选择没有 PLL 的时钟缓冲器。

图 5:振荡器 + 缓冲器架构

这种架构可行,但并非最佳解决方案。使用时钟发生器要优雅得多。特别是 SiTime 时钟发生器,它在一个小型 QFN 封装中集成了 MEMS 谐振器、时钟生成、时钟分配等更多功能。有关汽车时钟发生器的信息,请联系 SiTime。

独立时钟参考,无扩频(SRNS)

在 SRNS(独立参考,无扩频)架构中,诸如振荡器之类的不同时钟源被用于为根联合体和每个端点提供时钟。根据 PCI-SIG 规范,时钟频率必须为 100 MHz,最大允许偏差为±300 ppm(包括初始精度+温度范围内的稳定性)或±100 ppm(对于 PCIe Gen 5 及以上版本)。

例如,对于两个振荡器(PCIe Gen 1 至 Gen 4),最大允许频率偏差分别为±600 ppm,每个振荡器为±300 ppm。

图 6:SRNS 架构

在设计中,当更倾向于使用振荡器而非时钟发生器时,这是首选的架构。SiTime SiT9396 在-40°C 至+125°C 范围内具有低抖动和±50 ppm 的稳定性,支持 PCIe Gen 1 至 Gen 6 的 SRNS。

独立时钟参考,具有独立扩频(SRIS)

从 PCIe Gen 4 开始,PCI-SIG 规范包含了 SRIS(独立参考,独立扩频)的规定。引入这种架构的主要原因是,当端点远离根复合体时,避免为时钟配备电缆。然而,在大多数汽车系统中,根复合体和端点在同一块板上。在这种架构中,使用不同的时钟源(通常是振荡器)可以同时实现扩频。因此,最大允许的频率差为±5600 ppm。PCIe 发送器会在链路中插入虚拟数据,以处理发送器和接收器之间的时钟频率(换句话说,链路速度)差异。请注意,要么根复合体,要么端点,可以激活 SSC,但不能两者同时激活。与普通时钟架构相比,SRIS 架构对时钟抖动引入了额外的限制。SiTime 设备支持 SRIS 架构

图 7:SRIS 架构

SiTime 优势

SiTime 定时解决方案支持 PCIe Gen 1 至 6,并支持普通时钟、SRNS 和 SRIS 架构,同时提供了一些对于汽车和功能安全应用特别重要的优势。它们提供了更高的可靠性、更好的稳健性和小尺寸。

• SiTime 时钟发生器具有内部 MEMS 谐振器,不需要外部参考,消除了晶体谐振器所代表的“薄弱环节”。

• 出色的可靠性(< 0.5 FIT,< 0.1 DPPM)——比基于晶体的设备可靠多达 50 倍。

• 对冲击和振动的抵抗能力比基于晶体的设备强多达 10 倍。晶体谐振器中的冲击,尤其是振动,会增加生成时钟的抖动,从而增加 PCIe 链路上的误码率(BER)。晶体中的冲击和振动还会造成频率微跳和活动下降,从而降低 BER。SiTime 设备不存在这些问题

了解有关汽车级MEMS硅晶振的更多信息

了解有关SiT9396的更多信息

了解更多MEMS振荡器选型手册的信息

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483