SiTime差分振荡器的端接建议

1 简介

差分振荡器用于高性能应用,具有多种优势,例如对电源噪声具有更高的鲁棒性。表1中列出的SiTime差分振荡器系列提供了端接建议,带有LVPECL、LVDS或HCSL输出驱动器。 还讨论了用LVPECL输出驱动CML或HCSL时钟输入的接口。

|

产品系列 |

产品分类 | 信号模式 |

|

SiT9120 |

低成本差分振荡器 |

LVPECL,LVDS |

|

SiT9121 |

低成本差分振荡器 |

LVPECL,LVDS |

|

SiT9122 |

低成本差分振荡器 |

LVPECL,LVDS |

|

SiT9365 |

超低抖动差分振荡器 |

LVPECL,LVDS,HCSL |

|

SiT9366 |

超低抖动差分振荡器 |

LVPECL,LVDS,HCSL |

|

SiT9367 |

超低抖动差分振荡器 |

LVPECL,LVDS,HCSL |

|

SiT9386 |

汽车级差分振荡器 |

LVPECL,LVDS,HCSL |

|

SiT9387 |

汽车级差分振荡器 |

LVPECL,LVDS,HCSL |

|

SiT3821 |

低成本压控差分振荡器 |

LVPECL,LVDS |

|

SiT3822 |

低成本压控差分振荡器 |

LVPECL,LVDS |

|

SiT3372 |

低抖动压控差分振荡器 |

LVPECL,LVDS,HCSL |

|

SiT3373 |

低抖动压控差分振荡器 |

LVPECL,LVDS,HCSL |

2 LVPECL输出

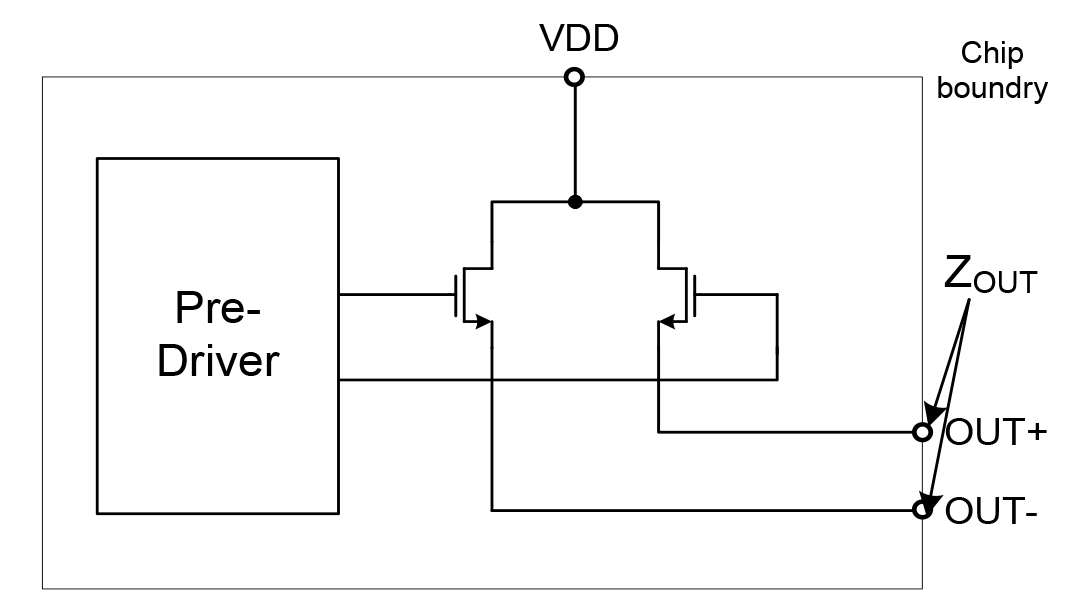

图1显示了用于SiTime差分振荡器系列的低阻抗LVPECL驱动器结构。驱动器的输出级由一对共源配置的NMOS晶体管组成。 典型的驱动器阻抗约为5Ω至10Ω。

图 1:LVPECL 驱动器输出结构

2.1 直流耦合应用的端接建议

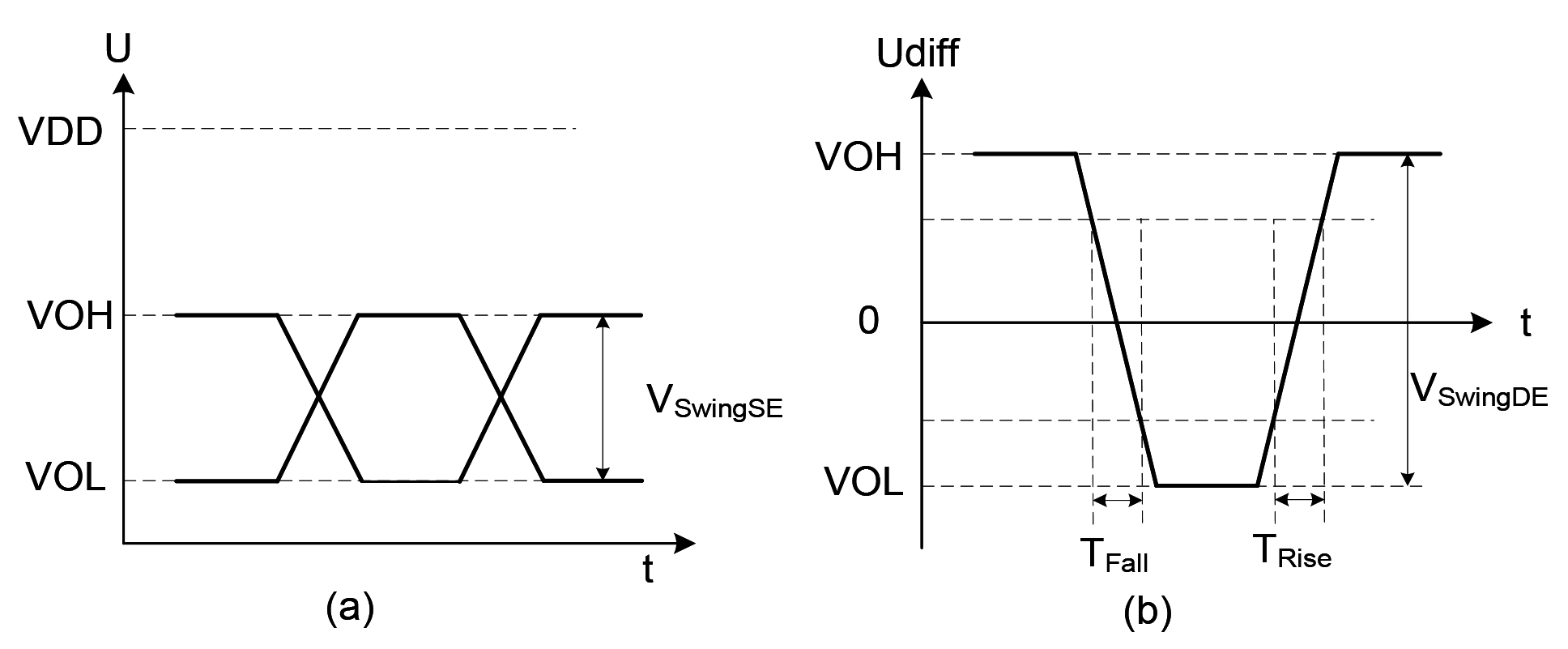

LVPECL 通常在负载侧端接,如图 2 所示。输出通过 50Ω 电阻连接到端接电压 (VT),为传输线提供良好的阻抗匹配(有关负载端接分析,请参见附录 A)。 图 3(a) 说明了具有典型端接的 LVPECL 输出的单端波形。 典型的电压输出高 (VOH) 和电压输出低 (VOL) 信号电平分别为VDD–0.9V 和VDD–1.7V。 数据表中规定的 VOH 和 VOL 限制考虑了不同部件之间的输出驱动器阻抗变化和外部负载条件。

正负输出之间差分波形的电压摆幅(VDiff = VOUT+ - VOUT-)是单端信号电压幅度的两倍。 典型的 LVPECL 差分摆幅为 1.6V。 图 3(b) 说明了如何为差分波形定义 20% 到 80% 的上升和下降时间。

请注意,VOH、VOL 和电压摆幅取决于终端,如果使用非默认终端,则可能不同。

图 2:具有直流耦合并联并联负载端接的 LVPECL

图 3:典型端接时的 LVPECL 逻辑电平

如果 LVPECL 接收器没有内置终端,外部 50Ω 终端电阻应尽可能靠近接收器放置,以减少可能导致信号完整性问题的未终端短截线。 传输线应仅在负载侧端接。

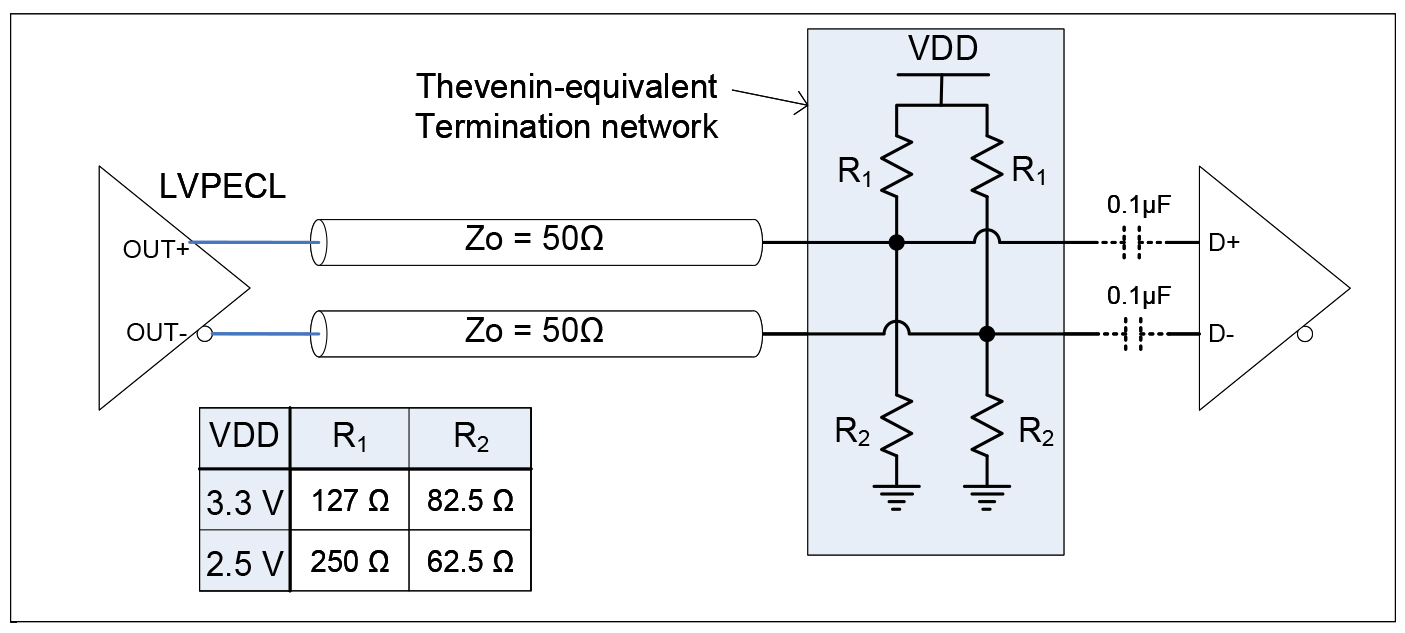

在不容易获得单独端接电压的应用中,可以使用形成戴维南等效网络的上拉和下拉电阻器来端接 50Ω 传输线(见图 4)。 这样的网络在接收器输入端建立了 VDD – 2V 的直流偏置电压和有效的 50Ω 终端阻抗。 请注意,3.3V 和 2.5V 电源电压的电阻值不同。

图 4:具有戴维宁等效网络的 LVPECL 直流耦合负载端接

图 5:具有 Y 偏置端接的 LVPECL

在大多数情况下,戴维南等效端接效果很好,但如果走线之间或差分对每一侧的电阻网络之间存在任何明显不匹配,或者如果接收器对共模噪声过于敏感,则它可能对电源噪声敏感。图 5 显示了 Y 偏置端接网络,它提供 VDD – 2V 的有效端接电压,无需连接到 VDD 或访问额外的端接电压源。 端接电压由通过电阻器 R3 的差分对电流之和产生。 电容器 C1 用于在端接电压下建立交流接地。

2.2 交流耦合应用的端接建议

图 6:具有交流耦合终端的 LVPECL

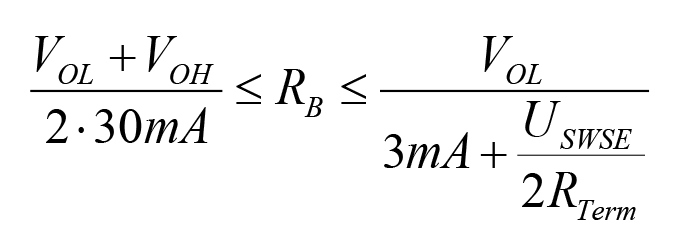

LVPECL 接收器可以是直流耦合或交流耦合。 如果接收器侧和振荡器侧的直流偏置电压不同,则需要交流耦合电容器。 在某些情况下,终端网络必须是 AC 耦合的,如图 6 所示。为了正确运行 LVPECL 驱动器,其输出晶体管不应完全关闭,因此需要在 AC 耦合电容器之前放置额外的偏置电阻器 RB 为驱动器提供直流电流路径。 RB 的值选择为使引脚处于低电平状态时通过驱动器引脚的最小电流不小于 3 mA,通过驱动器的最大直流电流不超过 30 mA。 公式1可用于估计RB。

公式1

公式1

在公式 1 中,USWSE 是单端电压摆幅,RTerm 是终端网络电阻。 SiTime 建议分别为 3.3V 和 2.5V 电源使用 100Ω 和 48.7Ω 的 RB 值。

应遵循以下建议,以通过 LVPECL 并行负载终端实现最佳信号完整性:

1. 将终端网络放置在距接收器 0.1 到 0.2 英寸的范围内。 将端接网络连接到接收器的长走线表现为短截线,会降低接收器输入端的信号完整性。

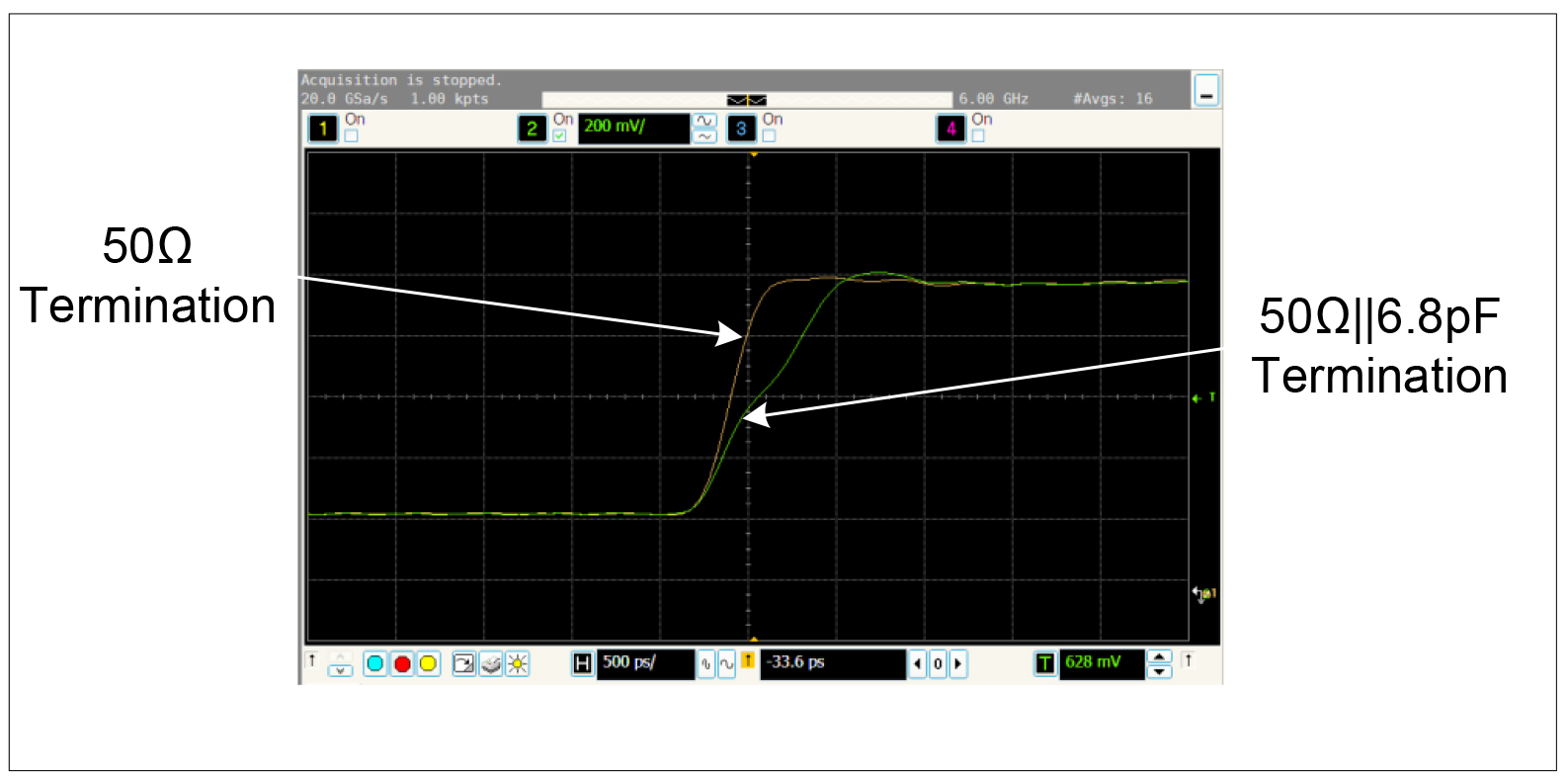

2. 最小化接收器输入端的容性负载。 当快速信号边缘到达接收器时,高容性负载会降低终端阻抗,从而导致大负载反射系数。 该反射在源处反射后稍有衰减地返回到负载。 经验法则是,如果 3Tr/(π·CL)<50Ω ,端接失配会变得很明显,其中 Tr 是 20% 到 80% 的上升时间,CL 是负载电容。 图 7 显示了 6.8 pF 寄生输入电容如何影响LVPECL 波形的上升沿的示例。

图7:寄生电容对SiT936x波形的影响

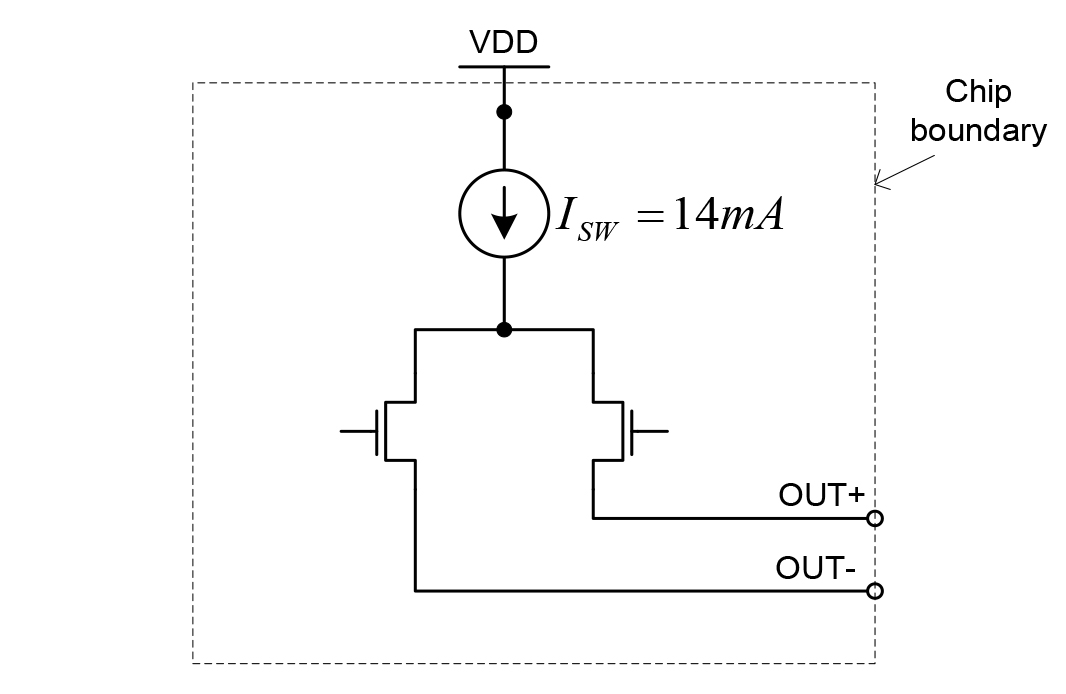

3 LVDS输出

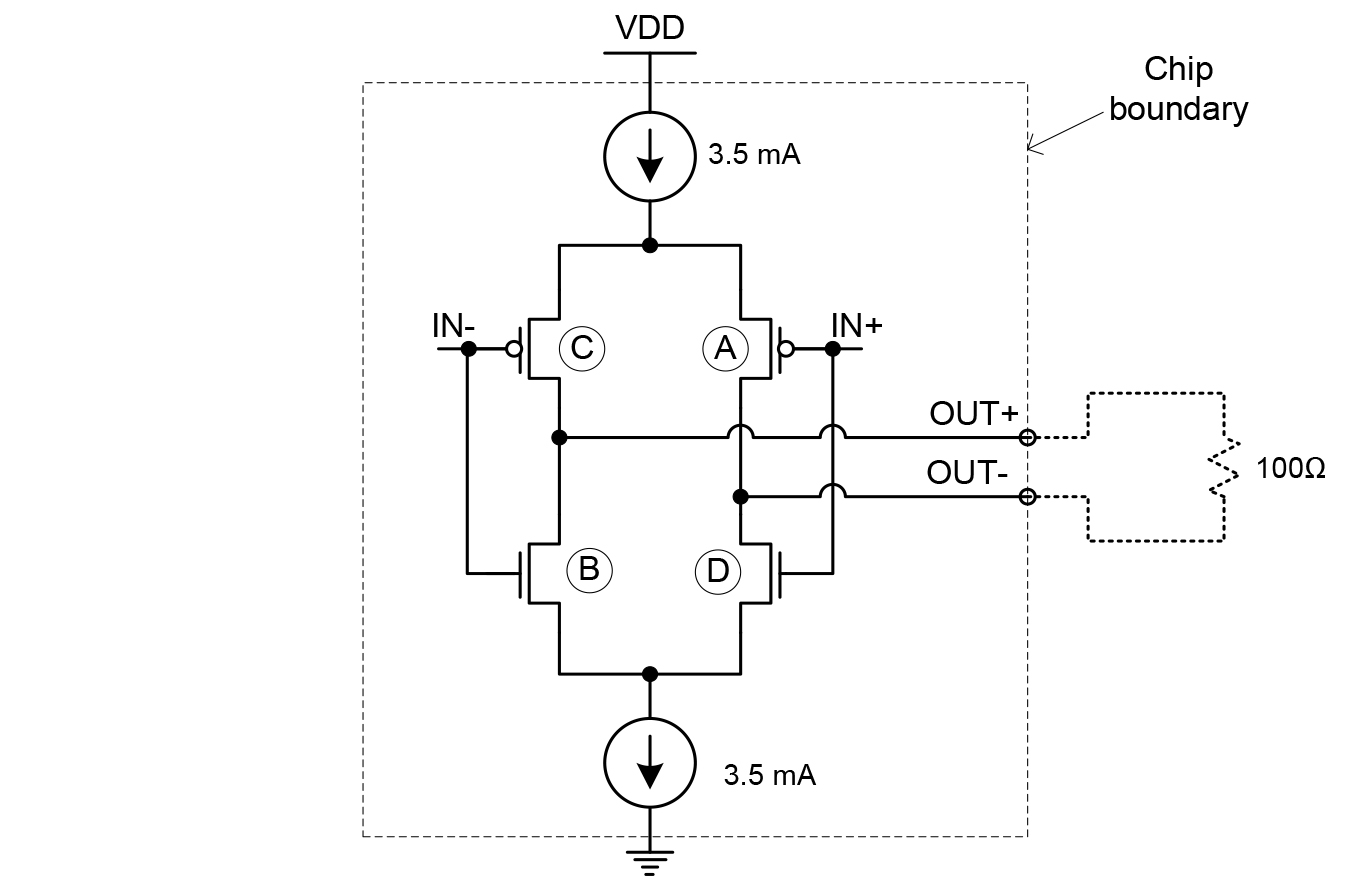

图8:LVDS驱动程序输出结构

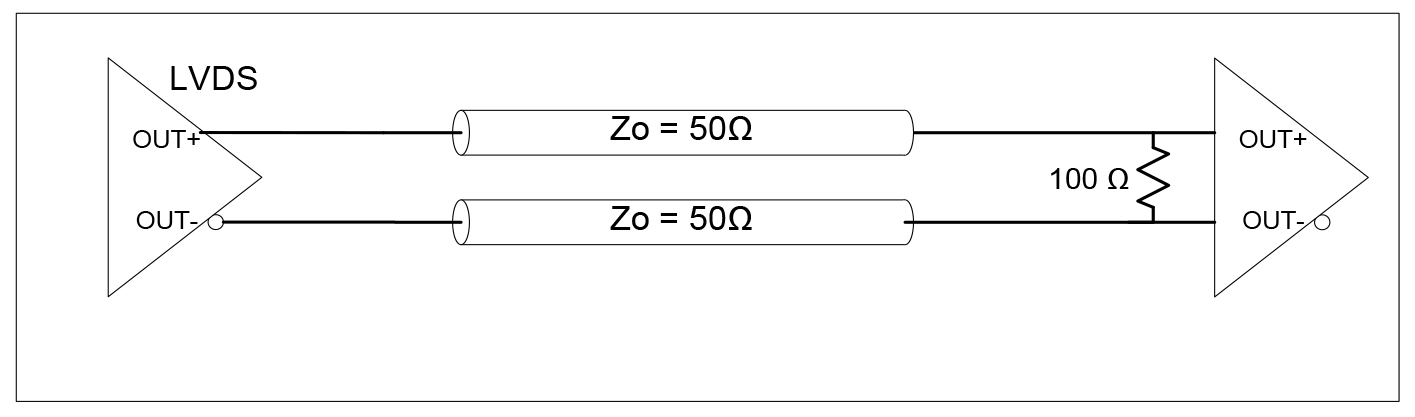

LVDS是一种高速数字接口,适用于许多需要低功耗和高抗噪性的应用。LVDS输出使用具有低电压波动的差分信号以高速传输数据。图8显示了LVDS驱动器的输出结构,包括通过开关网络(有时称为“H”开关)连接到差分输出的3.5 mA标称电流源。输出端通常连接到100Ω差分传输线,通过接收器输入端接一个100Ω电阻器。电阻值与传输线的阻抗匹配,并为信号提供电流路径。

驱动器包括将共模设置为1.2 V的电路,名义上与VDD无关。因此,不需要将驱动器外部偏置到任何特定电压。此外,LVDS输出可以连接到任何LVDS输入,而无需考虑振荡器的实际电源电压。

信号切换由标记为A、B、C和D的四个晶体管完成。由于接收器的阻抗通常较高,几乎所有来自驱动器的电流都流过100Ω电阻器,导致接收器输入之间的电压差为350 mV。在图8中,当信号In为低时,晶体管A和B接通;电流流过晶体管A和100Ω电阻器,并通过晶体管B返回。当信号IN为高时,晶体管C和D接通;电流流过晶体管C和100Ω电阻器,并通过晶体管D返回,从而在接收器上产生-350mV电压。

从接收器的角度来看,流过终端电阻器的电流方向决定了记录的是正差分电压还是负差分电压。正差分电压表示逻辑高电平,而负差分电压表示逻辑低电平。

3.1直流耦合应用的终端建议

图9:负载处的LVDS单直流终端

对于大多数应用,负载处的单个终端就足够了。在负载反射系数相对较高的情况下,双端接布置可减少整体往返行程(见图10)。在电源和负载上都有一个100Ω的电阻器,输出驱动器上的等效电阻降低到50Ω,导致输出信号摆幅减半。

图10:LVDS双直流终端

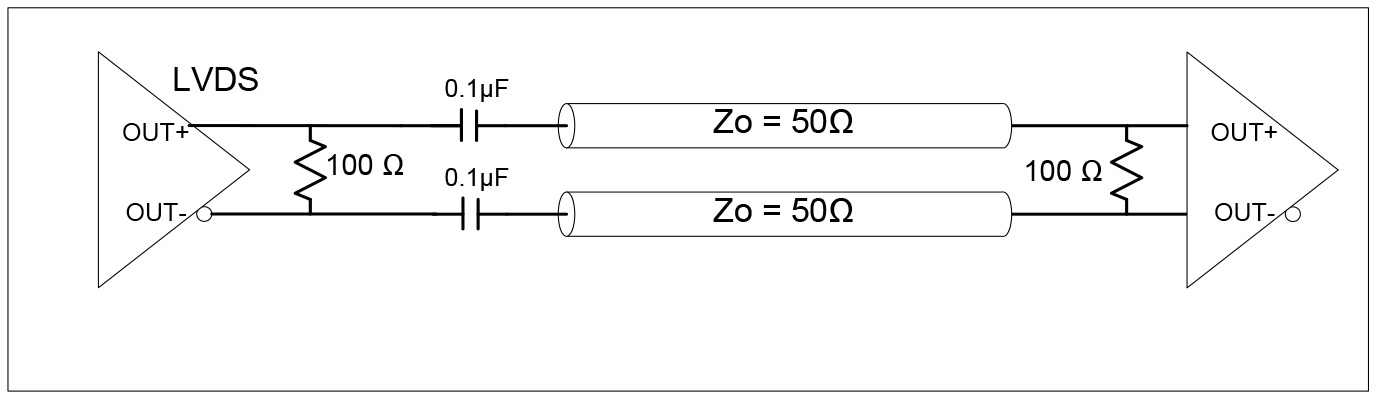

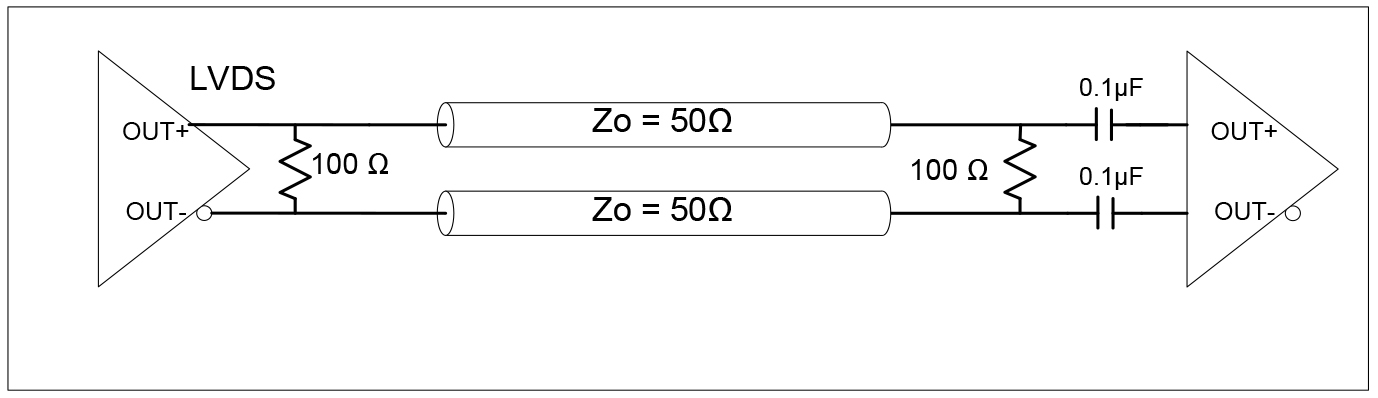

3.2交流耦合应用的终端建议

如果LVDS驱动器和接收器使用不同的共模电压工作,建议使用交流终端。电容器用于阻断来自驱动器的直流电流路径,因此接收器必须实现自己的输入偏置电路。

交流耦合可配置为负载处的单端或双端。单端接如图11所示。对于单端和双端,交流耦合电容器可放置在负载端接电阻器之前(如图12所示)或之后(如图13所示)。

图11:负载处的LVDS单交流终端

图12和图13所示的双端接仅在交流耦合电容器的位置不同。图12中的电容器由流过一半差动电阻的共模电流充电,这相当于50Ω。图13中的电容器由通过接收器输入电阻的电流充电,该电阻可以在几十K欧姆的范围内。在时钟启动期间,图12中所示的电容器充电速度比图13中所示的快得多。因此,有效的时钟信号将更快地提供给接收器。如果快速时钟启动很重要,则图12中所示的配置更可取。

图12:电容器靠近电源的LVDS双交流终端

在数据传输应用中,图13所示的配置可能更有利。由于其较高的RC时间常数,它可以维持更长的1s和0s的数据序列,而不会出现明显的电压降。

图13:电容器靠近负载的LVDS双交流终端

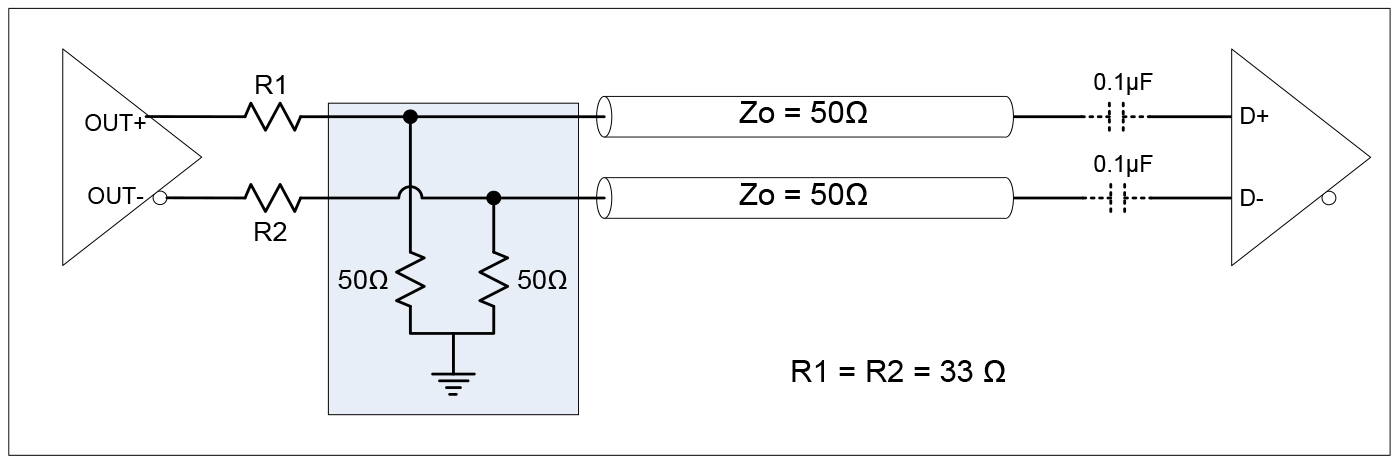

4 HCSL输出

图14:HCSL驱动器输出结构

HCSL驱动程序选项仅在某些SiTime振荡器系列中可用。HCSL输出结构(见图16和图14)由一个14 mA的开关电流源驱动,该电流源通常通过一个50Ω电阻器接地,如图15所示。标称信号摆幅为700 mV。输出端的开漏晶体管具有相当高的阻抗,范围为几千欧姆。从交流角度来看,输出晶体管阻抗与50Ω负载电阻器平行,因此等效电阻非常接近50Ω。由于该接口中使用的记录道具有50Ω的特性阻抗,因此从负载反射的任何信号都将在源处被吸收。通常,两个小电阻器R1和R2(见图15)与高阻抗驱动器串联放置。它们通过减缓输出电流的快速上升而起到超调限制器的作用,并且对电源处的阻抗匹配没有影响。SiTime建议这些电阻器为33Ω。

图15:HCSL接口终端

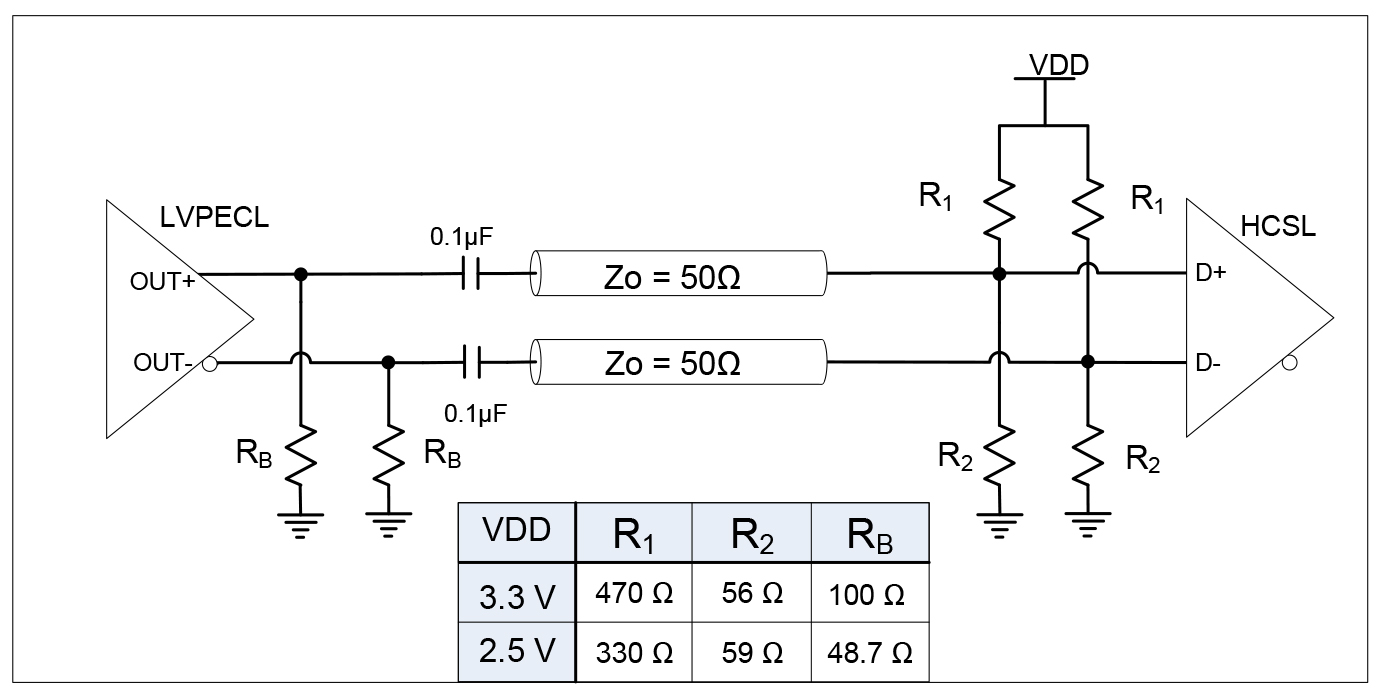

5 使用LVPECL振荡器驱动HCSL接收器

典型的HCSL接口使用电流模式驱动器,在源端使用50Ω至GND端接,在接收端不使用端接。此外,对于HCSL输出驱动器,LVPECL驱动器可用于驱动HCSL输入。图16显示了用于驱动具有LVPECL输出的HCSL接收器的推荐端接示意图。为了满足HCSL接收器所需的750mV VOH电平和0V VOL电平,它采用交流耦合电容器来分离电源和负载偏置电压。

负载侧的戴维南等效终端也在接收器输入端设置适当的共模电压。电阻器RB为LVPECL驱动器提供适当的直流偏置。2.5V和3.3V工作电压的推荐终端网络组件值如图16所示。

图16:LVPECL到HCSL接口

6 使用LVPECL振荡器驱动CML接收器

大多数SiTime差分振荡器没有CML输出选项,但它们可用于使用LVPECL驱动器驱动CML接收器。在这种情况下,终端示意图必须确保接收器输入端的400 mV单端电压摆动和VDD–200 mV共模电压[2]。图17显示了用于驱动具有LVPECL输出的CML接收器的推荐终端示意图。由于LVPECL和CML共模电压之间存在较大差异,因此需要配备用于直流电流隔离的耦合电容器。电阻器RB用于LVPECL驱动器的适当偏置。接收器端的戴维南等效终端设置适当的偏置电压,并与RB电阻器一起确保适当的信号摆动。

图17:LVPECL到CML接口

7 驱动自偏置差分输入

许多差分接收机具有片上直流偏置电路和/或终端网络。在这种情况下,振荡器输出应为交流耦合。如果需要外部偏置,则应根据接收装置的数据表进行设计。

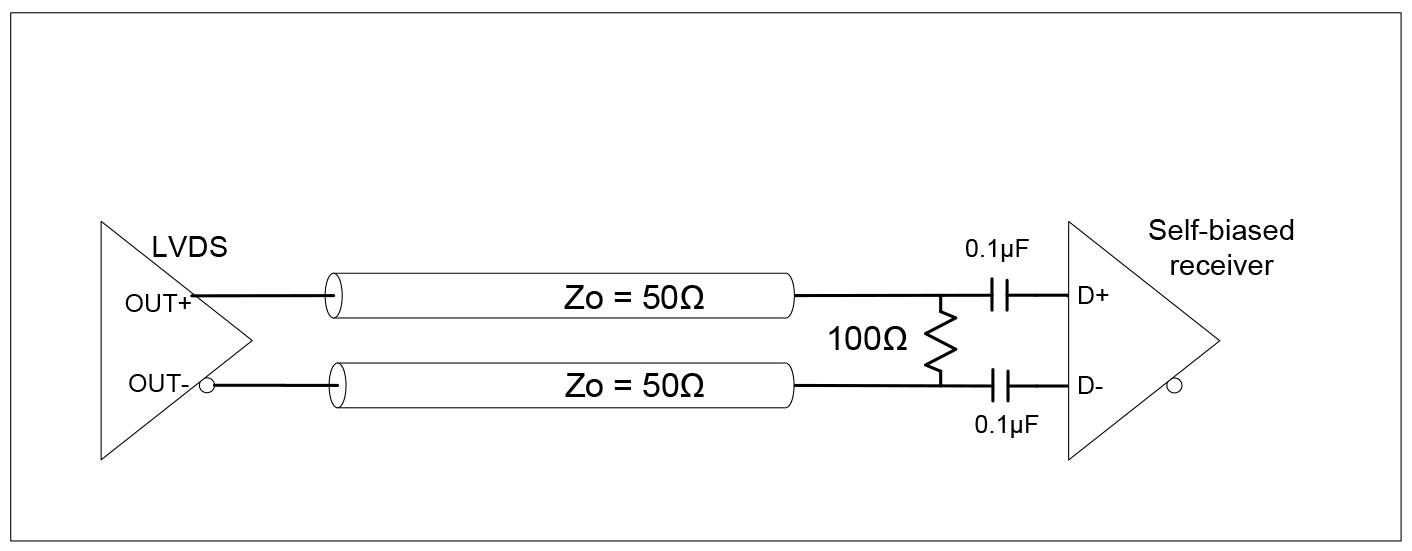

LVDS或LVPECL振荡器可用于驱动自偏置差分输入。LVDS输出需要更少的无源元件和更低的运行功率。如果700 mV的LVDS摆幅对接收器足够,则最好使用LVDS振荡器。图18显示了LVDS振荡器与自偏置差分接收机的接口。

图18:LVDS驱动器与带有内部终端和偏置的自偏置差分接收机的连接

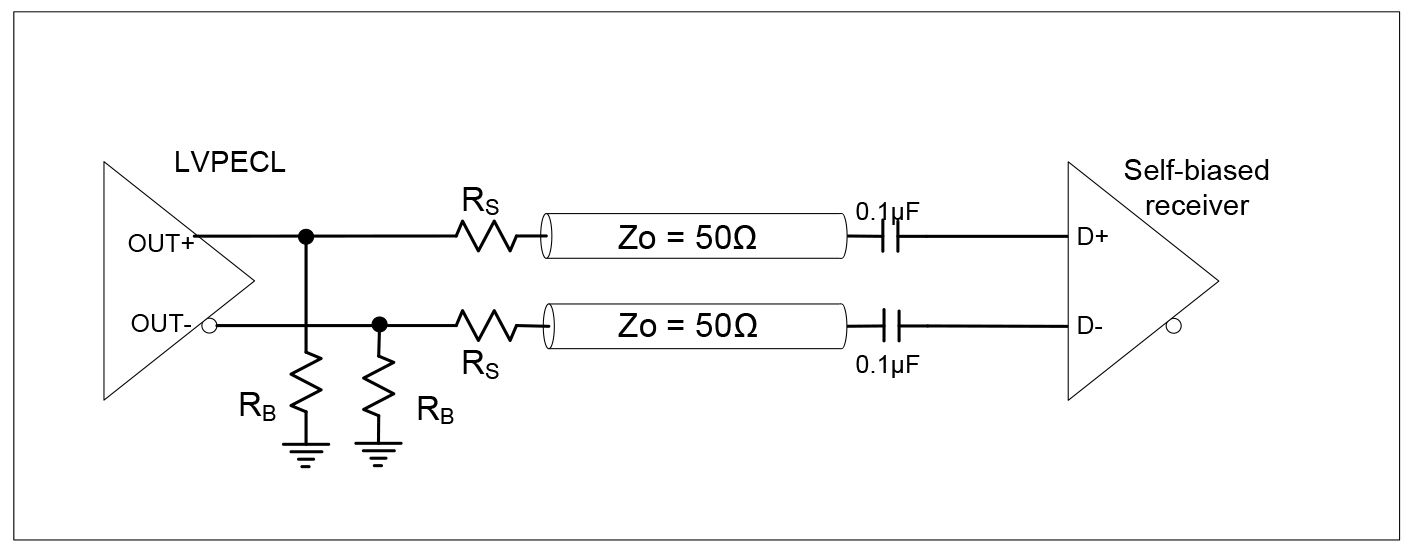

LVPECL输出可在接收器处产生高达1.6V的差分摆动。图19说明了将LVPECL振荡器连接至自偏置差分接收器的示意图。电阻器RS产生一个端接在负载侧的分压器。可通过选择RS值来设置接收器输入上的电压摆幅。RB为LVPECL驱动器提供直流偏置电流,其值可根据公式1计算。请注意,接收器将看到RS+50Ω的有效终端电阻值。

图19:LVPECL驱动器与带有内部终端和偏置的自偏置差分接收机的连接

为保持信号完整性,RS和RB应置于传输线之前,尽可能靠近振荡器。负载侧终端网络应尽可能靠近接收器输入。

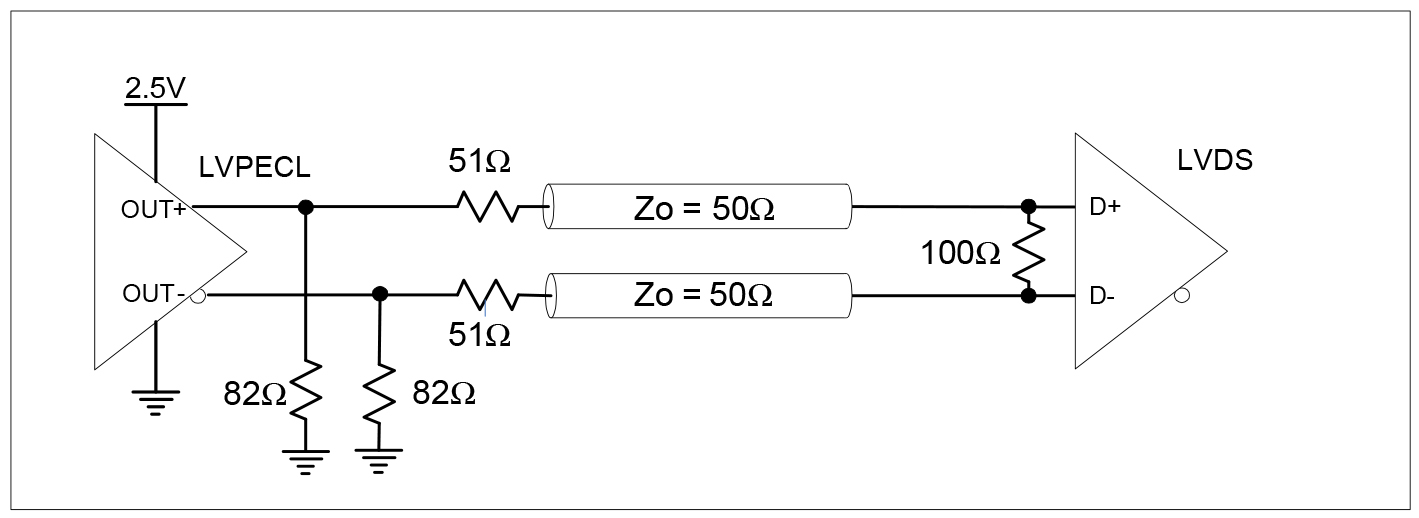

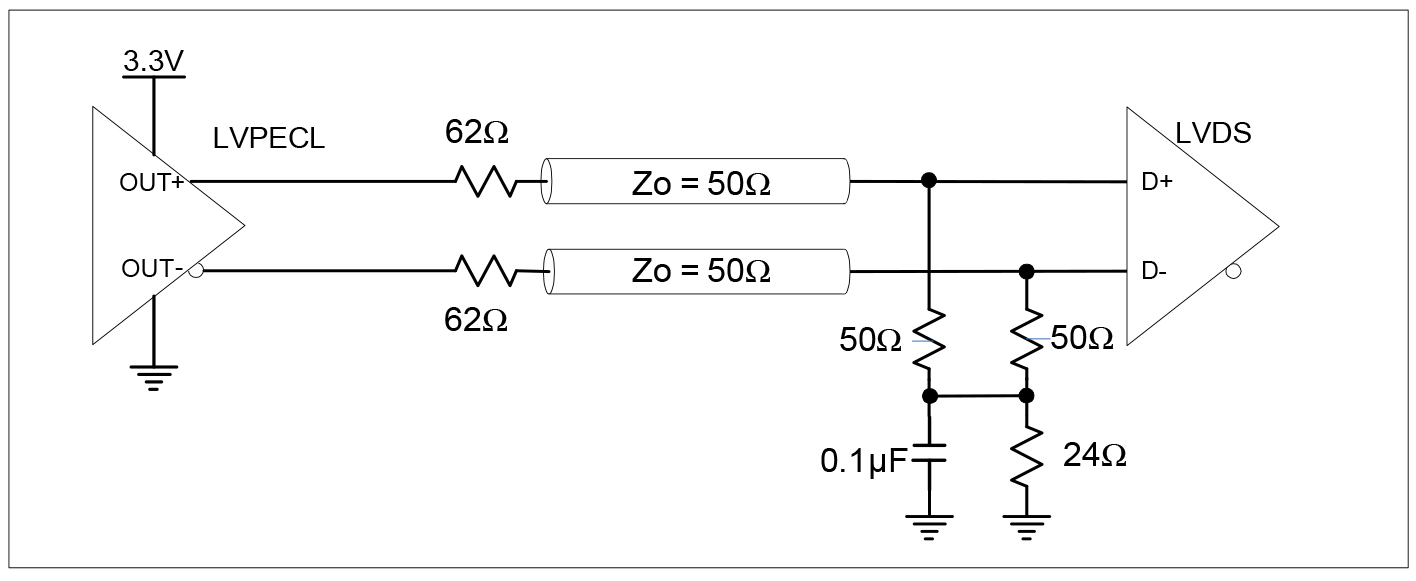

8 使用LVPECL驱动器驱动LVDS接收器

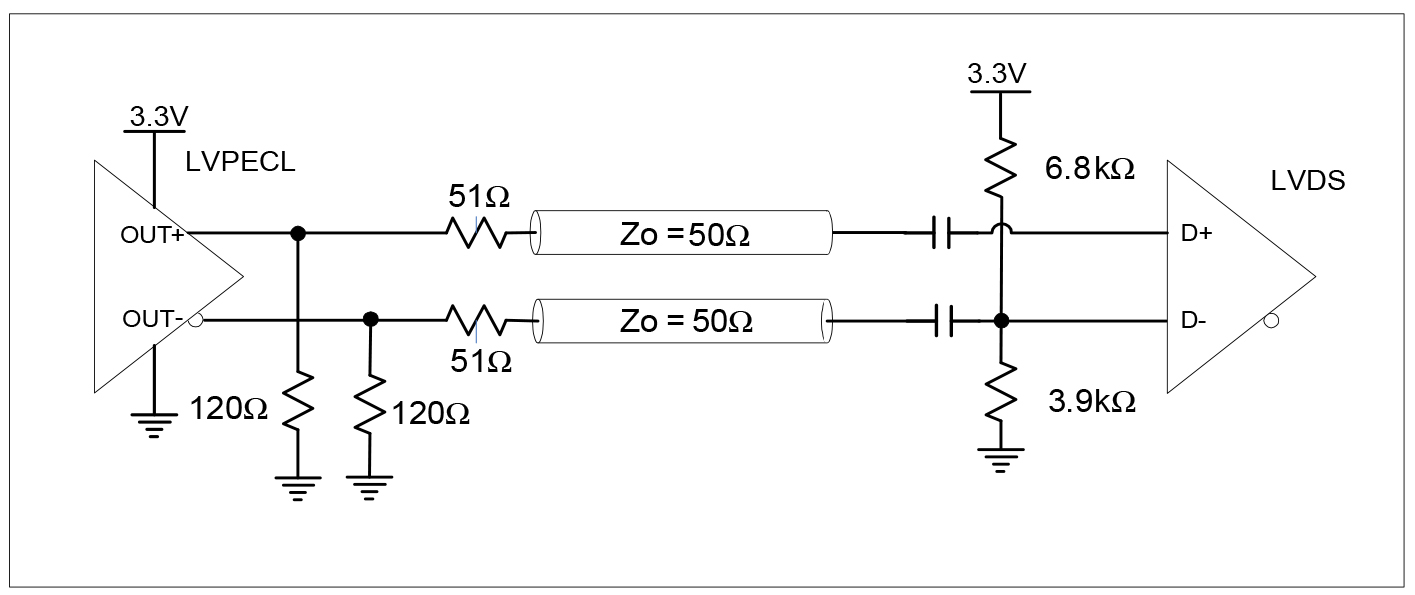

图20:将带有2.5 V VDD的LVPECL驱动器连接到LVDS接收器

在3.3V VDD的情况下,LVPECL驱动器和LVDS接收器的共模电压不同。图21建议在LVPECL驱动器和LVDS接收器之间使用串联电阻器和Y端连接。

图21:将LVPECL驱动器与3.3 V VDD连接到LVDS接收器

如果接收器具有片上终端,建议使用交流耦合,如图22所示。共模由电阻分压器设置。由于其等效电阻过高,不会导致正负输入之间的不平衡,因此只有一个输入偏置。

图22:将带有3.3V VDD的LVPECL驱动器连接到带有内部终端的LVDS接收器

9 将LVCMOS振荡器与LVDS/LVPECL输入接口

在某些情况下,需要使用单端输出源的时钟差分LVDS或LVPECL接收机。LVCMOS输出可以通过将交流信号连接到一个差分输入管脚并向另一个管脚施加直流阈值电压连接到LVDS或LVPECL接收器。为了满足差分摆幅要求,接收器侧单端时钟的振幅必须是LVDS或LVPECL接口差分摆幅的两倍。参考接收器数据表,确保输入电压在可接受范围内。

与差分振荡器相比,使用单端振荡器驱动LVDS/LVPECL输入可提供更低的功耗,但会降低抗噪性。

将单端输出连接到差分接收机需要以下条件:

1. 对于所有VDD的LVDS,输入端的共模电压应为1.2V;对于2.5V VDD的LVPECL,输入端的共模电压应为1.2V;对于3.3V VDD的LVPECL,输入端的共模电压应为2V。

2. LVDS的输入电压摆幅应为700mV至800mV,LVPECL的输入电压摆幅应为1.2V至2V。

3. 终端电路的输入阻抗必须与跟踪阻抗匹配,以保持信号完整性。典型的轨迹阻抗为50Ω。

图23显示了在2.5V VDD下将单端输出连接到任何电压LVDS和LVPECL的推荐示意图。共模电压由输出驱动器阻抗和电阻器R1和R3产生的分压器设置。电容器C1提供从负极输入到接地的交流信号路径。正输入端的信号振幅由分压器设置,分压器由与R1串联的输出驱动器电阻和与R3并联的R2组成。

图23:将LVCMOS驱动器连接到2.5V/3.3V LVDS或2.5V LVPECL接收器

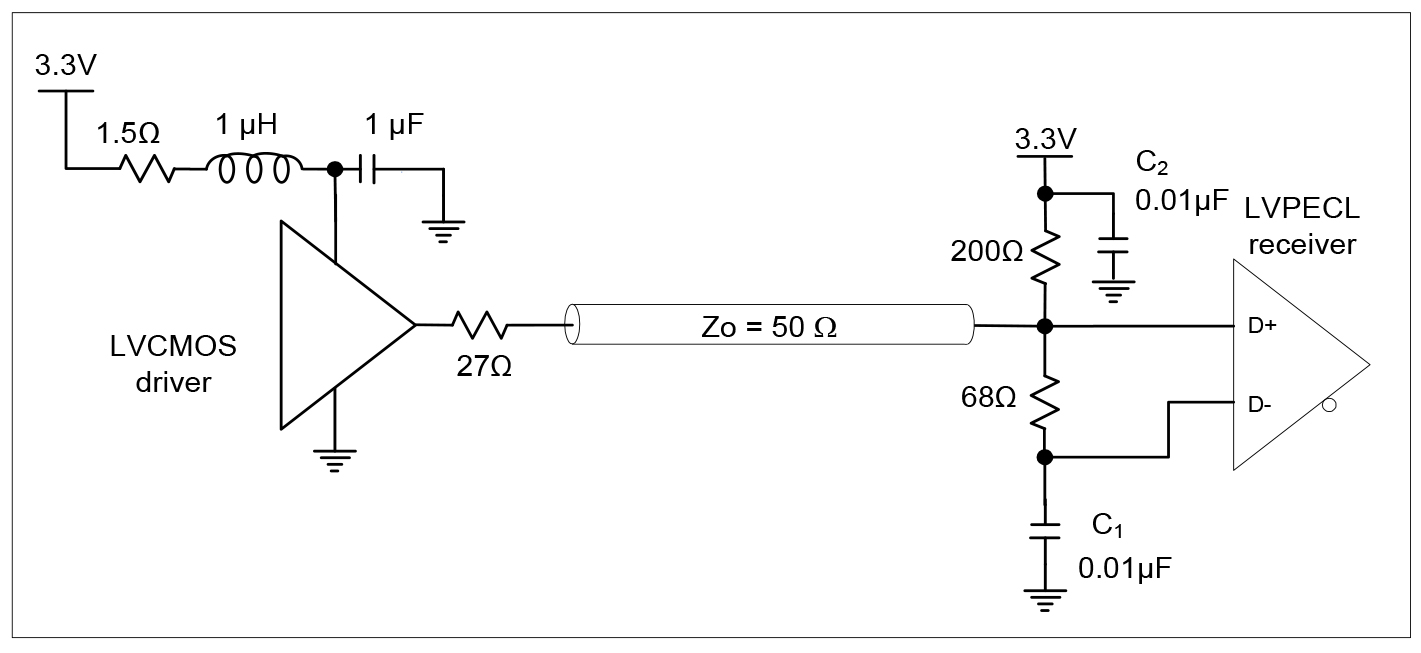

图24显示了在3.3V VDD下将LVCMOS连接到LVPECL的示意图。接收器侧的共模电压由输出驱动器阻抗与27Ω电阻器和200Ω上拉至VDD串联而成的分压器设置。

图24:以3.3V VDD将LVCMOS驱动器连接至LVPECL接收器

图23和图24中的推荐组件值是基于25Ω LVCMOS驱动器阻抗计算的。该值对应于LVCMOS振荡器SiT8008系列的典型驱动器阻抗。

LVCMOS振荡器在其电源网络中有一个RLC滤波器,如图23和图24所示。SiTime建议使用此RLC滤波器,因为它可以显著提高电源噪声抑制能力。

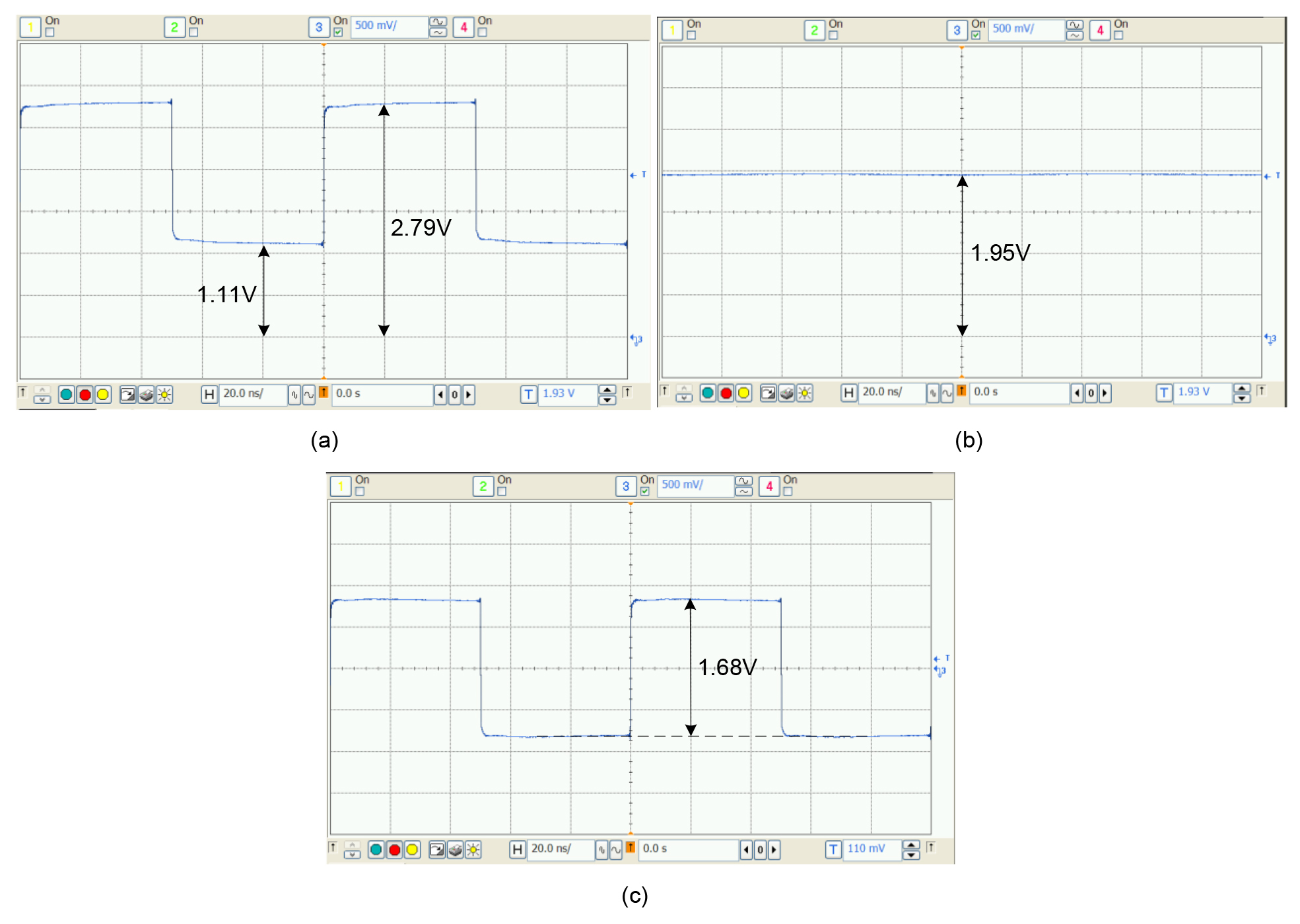

图25显示了使用单端时钟驱动时3.3V LVPECL接收器输入端的波形示例。

图25:3.3V VDD LVPECL接收器正(a)、负(b)输入端的波形以及由此产生的差分波形(c)。

10 结论

本应用说明介绍了SiTime差分振荡器的输出驱动器结构,以及LVPECL、LVDS和HCSL差分输出最常用的交流耦合和直流耦合终端方案。讨论了具有LVPECL输出的HCSL和CML接收机接口的推荐选项。还提出了允许使用单端LVCMOS振荡器驱动LVDS或LVPECL时钟接收器的端接方案。通过广泛的输出类型选择,用户可以选择最适合其要求的输出信号。

附录A:传输线终端阻抗匹配

当印刷电路板(PCB)或电缆的电长度大于发射到该线路的信号的20%-80%上升时间的一半时,该线路的任何线路都可以作为传输线。正确的端接是实现最佳信号完整性的一个重要因素。本附录讨论了源、负载和双端接策略。

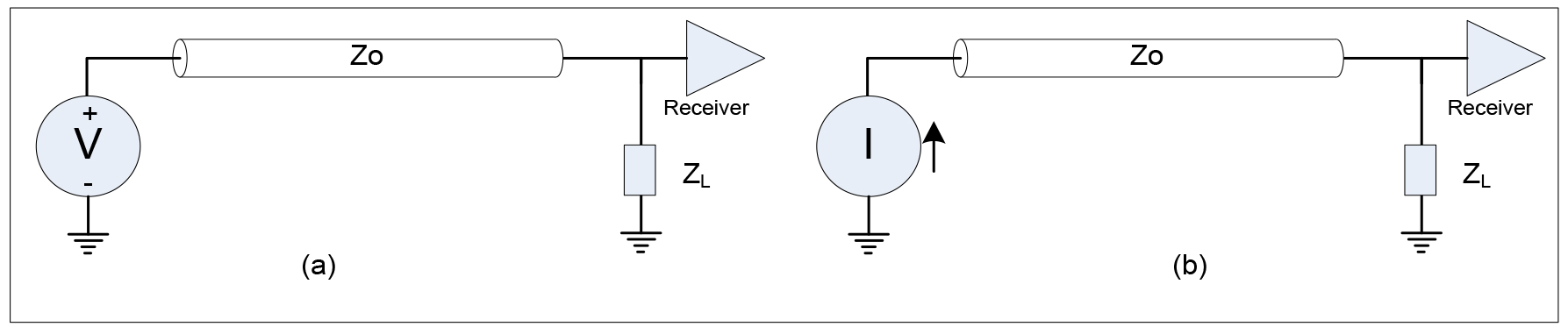

A.1 负载终止

图26:传输线平行负载端接

图26显示了由电压或电流源信号驱动的以Lz并联负载阻抗终止的传输线。一旦信号到达线路另一侧的负载,其部分能量将被负载吸收,其余能量将反射回电源。反射信号与入射信号之比称为反射系数,计算如下:

公式2

公式2

如果负载端接阻抗与记录道相同,即ZL=ZO,则TL=0,这意味着没有反射信号。如果负载阻抗与记录道阻抗不匹配,一些信号将反射回源。反射信号的一部分,一旦到达源,可根据源反射系数再次反弹到负载,计算如下:

公式3

公式3

在负载处看到的总反射是通过传输线的往返反射的结果,可使用往返反射系数TRT进行计算,计算如下:

![]() 公式4

公式4

较大的反射系数值会导致信号裕度减小、过度振铃和接收器输入端的额外触发边缘。因此,应尽量减少往返反射,以在接收器端实现最佳信号完整性。

对于图26(a)中的理想电压驱动器,ZS=0,这导致TS = -1。对于图26(b)中的理想电流驱动器,ZS = ∞ , 这导致TS = +1。在这两种情况下,到达源的反射信号中的所有能量将再次反射回负载。因此,匹配良好的负载阻抗是减少反射信号的最有效方法。

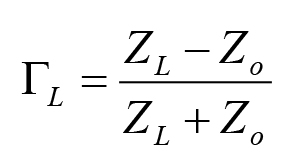

A.2 源端接

图27:传输线源端接

在某些应用中,很难在负载处正确终止传输线。这可能是由于负载阻抗不受控制或无法将终端靠近线路末端的接收器电路。在这种情况下,可以使用图19(a)和图27(b)中所示的源终止策略。假定接收器具有高阻抗,这导致负载反射系数为1(TL = +1)。信号将反射到信号源。如果源阻抗与ZO匹配,则反射的大部分能量可被源阻抗吸收。往返反射系数将为TRT = TS。

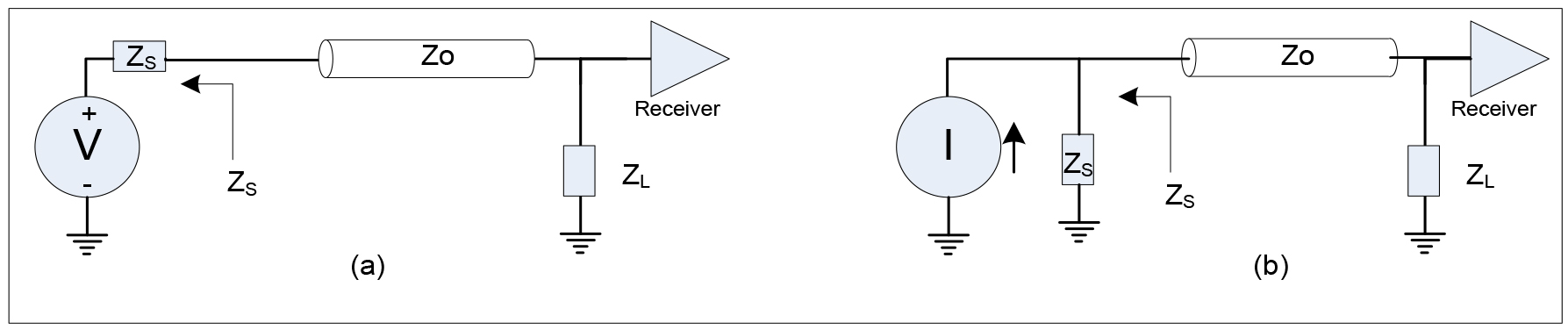

A.3 双重终止

图28:双端接技术

在某些应用中,可能难以将负载或源反射系数降低到可接受的较小值,例如,由于过多的寄生电容和电感。在传输线两端端接是减少往返反射和提高信号完整性的有效方法。图25显示了电压和电流驱动器的双端接。例如,如果TL = TS = 0.1,则TRT = 0.01,即,只有1%的信号反射回负载。

双端接的一个缺点是,到达负载的信号振幅将是单端接方案中信号振幅的一半。

- MEMS振荡器为何具有较高的耐久性和可靠性2024-07-19 15:01:537500

- 深入了解MEMS辅助温度传感器为何具有 20-µK 分辨率2024-07-18 10:39:036000

- SiTime具有 40 μK 分辨率的DualMEMS 谐振器时间数字转换器2024-07-17 11:21:013600

- 深入分析低带宽锁相环的高稳定性为何受控振荡器影响2024-07-16 18:02:338500

- ±0.01ppm高精度温补振荡器SiT5501如何改变边缘网络的精确计时市场2024-01-17 00:00:008870

- ±0.1ppm高精度温补振荡器SiT7910如何为航空航天和国防提供25倍精准计时2023-03-17 10:38:231433227

- 汽车级晶振选型设计指南2022-06-28 09:14:544800

- SiTime硅晶振在SSD存储中的应用2022-05-23 09:51:424400

- 示波器的两个最重要参数之示波器宽带和采样率详解2022-04-02 13:32:204000

- SiTime推出高性能XCalibur™有源谐振器SiT14082022-02-08 09:47:597922

- 汽车级晶振为自动驾驶ADAS保驾护航2021-08-20 13:39:175784

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483