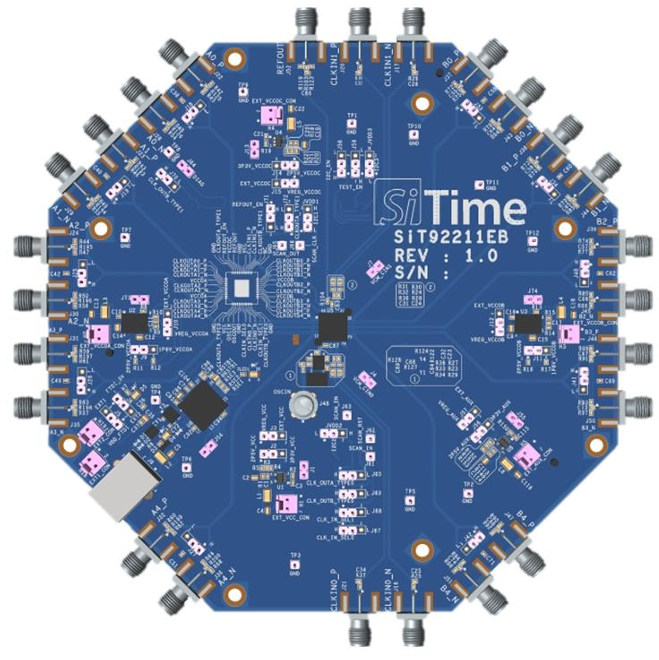

SiT92211 评估板 用于评估 2.1 GHz、10 差分输出和 1 LVCMOS 低抖动扇出缓冲器 SiT92211

SiT92211 评估板 (EVB) 硬件用户手册

1 、简介

SiT92211 评估板设计用于评估 2.1 GHz、10 差分输出和 1 LVCMOS 低抖动扇出缓冲器 SiT92211。

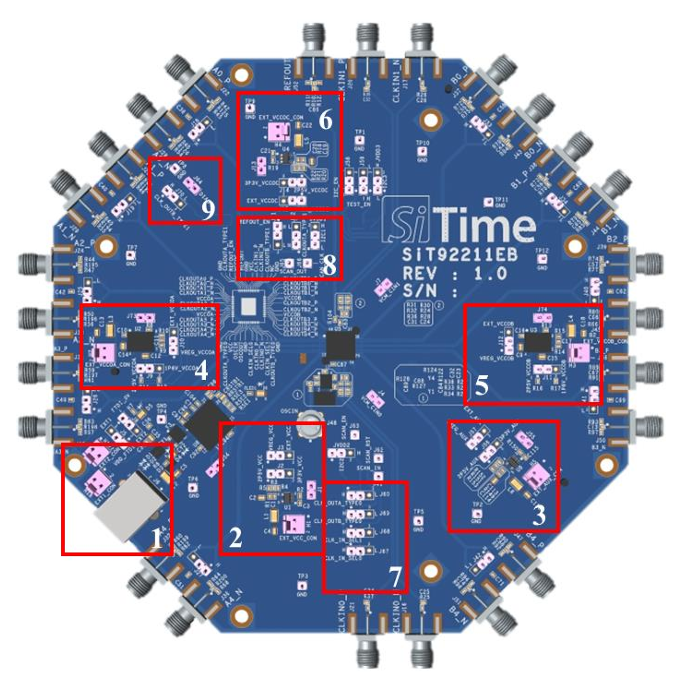

图 1. SiT92211 EVK 电路板

2 、特性

1) 50 fs RMS 的添加抖动性能。

2) 3:1 输入时钟选择。

3) 两个通用时钟输入,工作频率高达 2.1 GHz,可接受 LVPECL、LVDS、LVCMOS、CML、HCSL、SSTL 或单端时钟。

4) 一个晶体输入,可支持 8 MHz 至 50 MHz 频率范围内的晶体,也可接受单端输入时钟。

5) 两个输出驱动器组 A 和 B,可独立编程为 LVPECL、LVDS、HCSL 或 HIZ 模式。

6) 时钟输出之间的典型输出偏移为 30 ps。

7) 差分输出驱动器采用电平转换,核心电源电压为 3.3 V/2.5 V/1.8 V,输出电源电压为 3.3 V/2.5 V/1.8 V。

8) SiT92211 缓冲器由引脚控制。9) LVPECL/LVDS 模式具有高 PSRR -70/-73 dBc。

3 、功能说明

SiT92211 是一款 10 输出差分时钟扇出缓冲器,具有低附加抖动,工作频率高达 2.1 GHz。它具有一个 3:1 输入多路复用器(可选晶体振荡器输入)、两组 5 路差分输出(带多模式缓冲器(LVPECL、LVDS、HCSL 或 Hi-Z))、一个 LVCMOS 输出和 3 个独立的输出缓冲器电源。输入选择和输出缓冲模式通过引脚绑扎控制。该器件采用 48 引脚 WQFN 封装。

图 2. 功能框图

3.1. VCC 和 VCCO 电源

SiT92211 具有独立的 3.3/2.5/1.8 V 内核 (VCC) 和 3 个独立的 3.3/2.5/1.8 V 输出电源(VCCOA、VCCOB 和 VCCOC)。以 2.5/1.8 V 电压工作的输出电源可降低功耗,并与 2.5/1.8 V 接收器兼容。LVPECL (VOH, VOL) 和 LVCMOS (VOH) 的输出电平以各自的 VCCO 电源为基准,而 LVDS 和 HCSL 的输出电平在指定的 VCCO 范围内相对恒定。

3.2. 时钟输入

输入时钟可从 CLKin0/CLKin0*、CLKin1/CLKin1* 或 OSCin 中选择。时钟输入选择由 CLKin_SEL[1:0] 输入控制,如表 1 所示。

选择 CLKin0 或 CLKin1 时,振荡器断电。用户可以浮动 OSCin 和 OSCout 引脚,因为这些引脚内部是下拉的。OSCin 用 56 KΩ 电阻下拉。

表 1. 输入时钟选择

3.3. 时钟状态(输入状态与输出状态)

表 2. 输入与输出阶段

3.4. 输出驱动器类型

可分别使用 CLKoutA_TYPE[1:0] 和 CLKoutB_TYPE[1:0] 输入配置 A 组和 B 组输出的差分输出缓冲器类型,如表 3 所示。对于不需要所有差分输出的应用,任何未使用的输出引脚都应保持浮动,并尽量缩短铜长度,以最大限度地减少电容和潜在耦合,并降低功耗。如果不使用整个输出组,建议禁用(Hi-Z)该组以降低功耗。

表 3. 输出驱动器类型编程

3.5. 参考输出

参考输出 (REFout) 提供所选输入时钟的 LVCMOS 副本。LVCMOS 输出高电平以 VCCOC 电压为基准。如表 4 所示,可使用启用输入引脚 REFout_EN 启用或禁用 REFout。参考输出时钟与所选时钟内部同步。这就避免了在启用或禁用参考时钟时出现任何闪烁或运行脉冲。

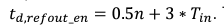

当 REFout_EN 从低电平变为高电平时,输出时钟会在延时 td 内启用,其中 td 由下式给出。

是输入时钟的时间周期。

是输入时钟的时间周期。

表 4. 基准输出使能

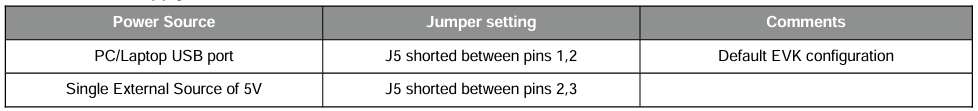

4 、电源连接

SiT92211 缓冲器有四个电源 VCC、VCCOA、VCCOB 和 VCCOC。VCCOA 电源是 A 组输出驱动器的专用电源。VCCOA 电源可以是 3.3 V+/-5%、2.5 V+/-5%、1.8 V+/-5%。VCCOB 电源是 B 组输出驱动器的专用电源。VCCOB 电源可以是 3.3 V+/-5%、2.5 V+/-5%、1.8 V+/-5%。VCCOC 电源是 LVCMOS 输出驱动器的专用电源。VCCOC 电源可以是 3.3 V+/-5%、2.5 V+/-5%、1.8 V+/-5%。VCC 电源专用于 SiT92211 内部的输入时钟接收器、时钟分配单元和 XO。该电源独立于 VCCOA、VCCOB 和 VCCOC。VCC 电源可在 3.3 V+/-5 %、2.5 V+/-5 % 和 1.8 V +/- 5 % 之间变化。

VCC、VCCOA、VCCOB、VCCOC 电源可按下表 5 设置。

表 5. SiT92211 EVK 的电源连接

注:有关跳线 J5 的连接,请参阅示意图表 6

将 USB 电缆从 PC/laptop USB 端口连接到 EVK 的 USB 接口。连接 USB 后,用户可以看到 LED D4 和 D5 发光。SiT92211 将使用板载 LDO,以 VCC=VCCOA=VCCOB=VCCOC = 3.3 V 电压启动。如表 6 所示,可使用跳线设置将 LDO 编程为不同的电压电平。

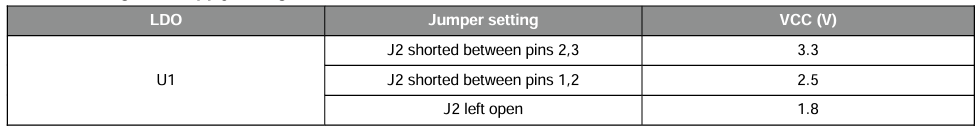

表 6 设置 VCC 电源电压

注释

1) 跳线 J2 的连接请参见电路图 1。

2) 在 EVK 的默认配置中,使用 U1 LDO 将 VCC 输出设置为 3.3V。

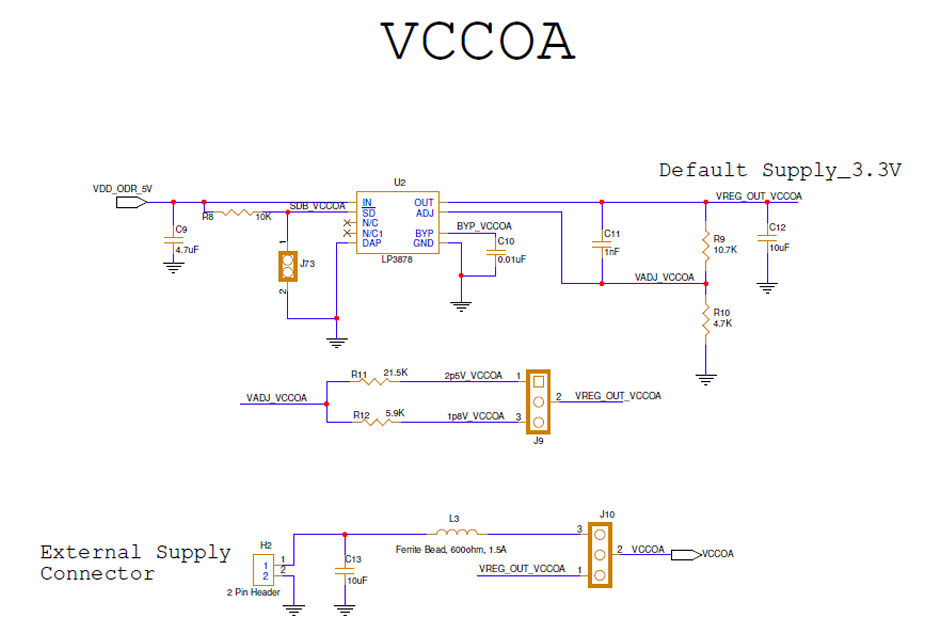

表 7. 设置 VCCOA 电压

注释

1) 请参阅示意图 2 或跳线 J9 连接。

2) 在 EVK 的默认配置中,使用 U2 LDO 将 VCCOA 设置为 3.3V。

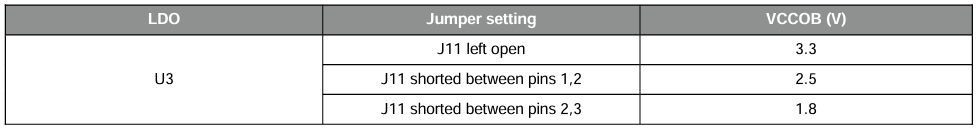

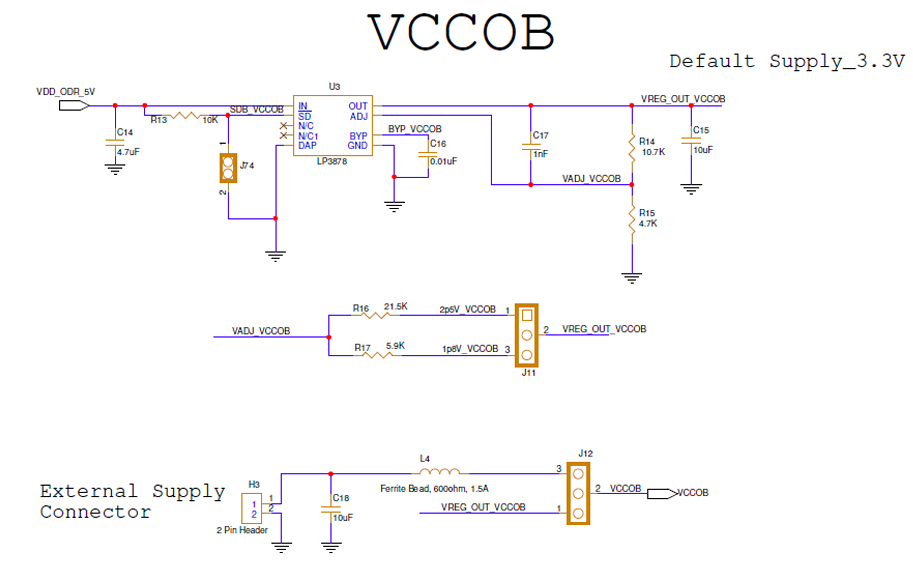

表 8. 设置 VCCOB 电压

注释

1) 跳线 J11 的连接请参见示意图页 3。

2) 在 EVK 的默认配置中,VCCOB 使用 LDO 设置为 3.3 V。

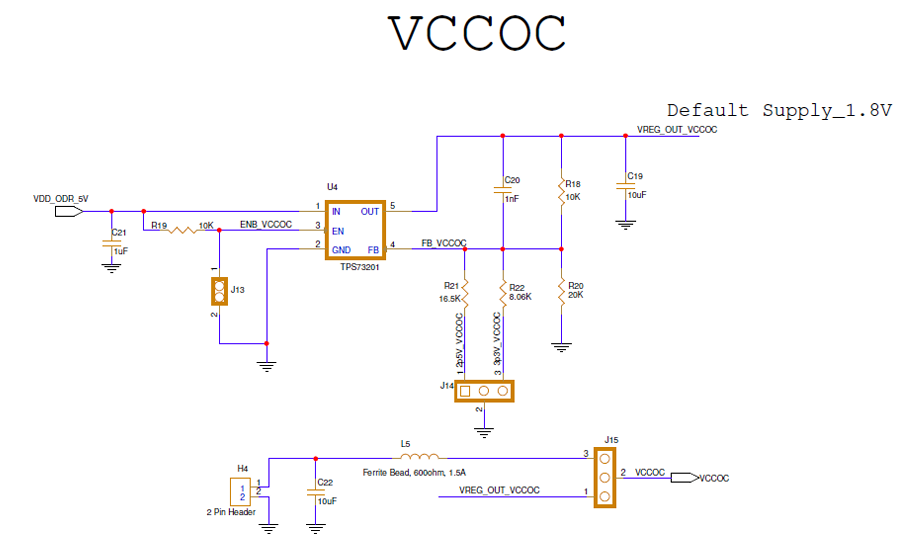

表 9. 设置 VCCOC 电压

注:

1) 跳线 J11 的连接请参见示意图页 4。

2) 在 EVK 的默认配置中,使用 U4 LDO 将 VCCOC 设置为 3.3V。

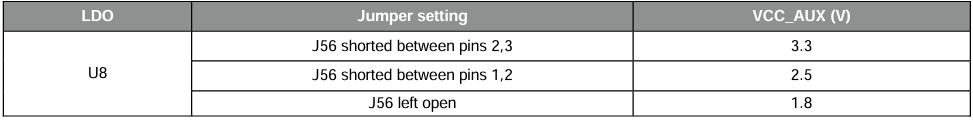

表 10. 设置 VCC_AUX 电压

注

1) 跳线 J56 的连接请参阅示意图页 5。

2) VCC_AUX 是电平转换器输出的电源,用于自动控制时钟选择、REFOUT_EN 引脚、ODR 类型。保持 VCC = VCC_AUX 3.

3) 在 EVK 的默认配置中,使用 U8 LDO 将 VCC_AUX 设置为 3.3V。

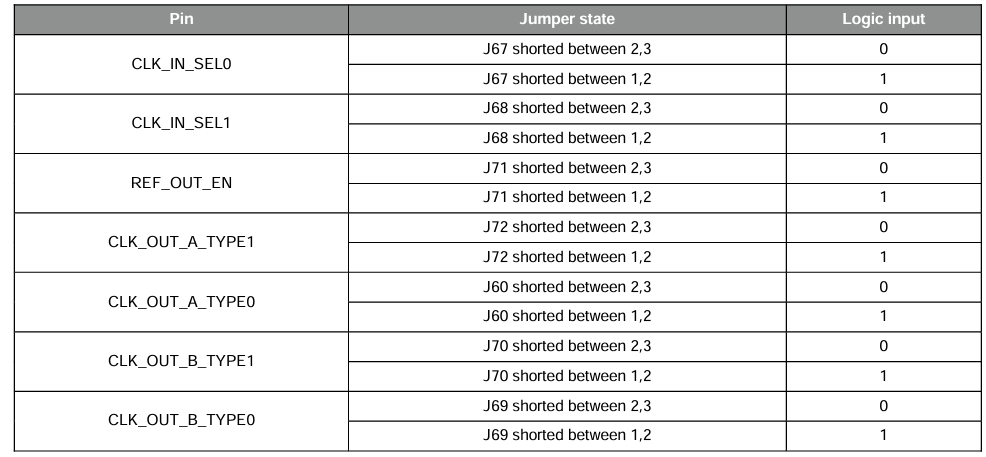

5 、在 EVK 中设置输入时钟选择和 REF 输出使能

用于控制输入时钟选择和输出使能的跳线设置如下。

表 11. 控制时钟选择和输出启用的跳线设置

注释

1) 输入时钟选择编程如下。

a. 输入时钟选择编程:2'b00 - clock0,2'b01 - clock1,2'b10 - XO

2) 跳线 J61、J62 的连接请参阅原理图 8。

3) REF_OUT_EN 的编程如下

a. REF_OUT_EN 编程:1'b0 - 输出禁用,1'b1 - 输出启用

4) 有关跳线 J71 的连接,请参阅示意图 8。

5) A 组的 odr 类型编程如下。

a. ODRA 类型编程:2'b00 - LVPECL、2'b01 - LVDS、2'b1HCSL、2'b11 - HIZ

6) 跳线 J72、J60 的连接请参见示意图 8。

7) A 组的 odr 类型编程如下

a. ODRB 类型编程:2'b00 - LVPECL,2'b01 - LVDS,2'b10 - HCSL,2'b11 - HIZ

8)跳线 J64、J63 的连接请参见示意图 8。

9) J58 和 J59 跳线应始终保持默认状态:位于引脚 2 和引脚 3 之间。

10) 标有 JVDD1、JVDD2、JVDD3、Diag 的跳线应保持默认状态:浮动。

11) J8 应保持默认状态:位于引脚 1 和引脚 2 之间,以便为板载 LDO 供电。

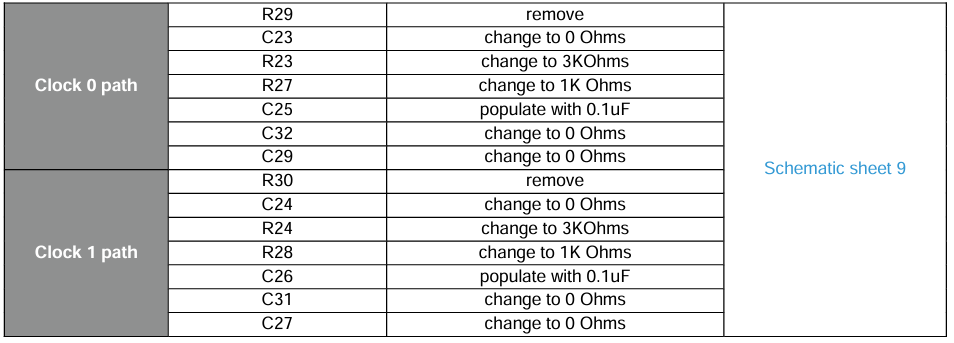

6、 输入时钟配置

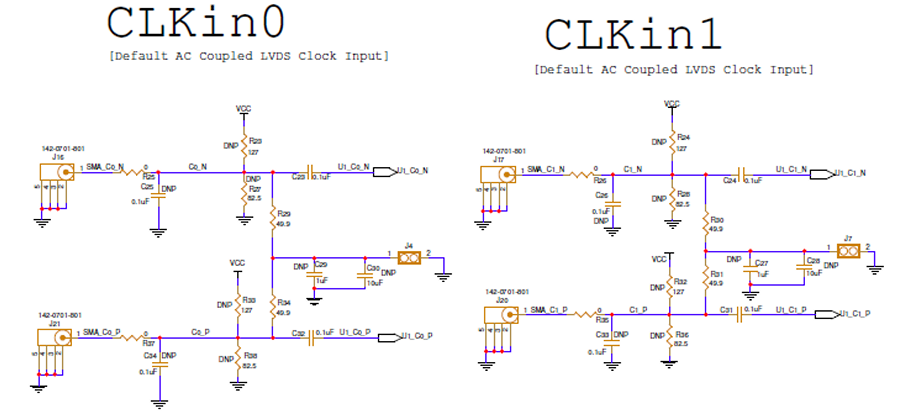

输入时钟采用交流耦合,并以差分 100 欧姆端接。因此,如原理图 9 所示,EVK 配置为差分输入时钟。

图 3 输入时钟配置

7、 配置单端交流耦合输入时钟

许多应用要求缓冲器接收单端输入时钟。因此,需要对 EVK 做一些最小的改动,以实现单端操作。

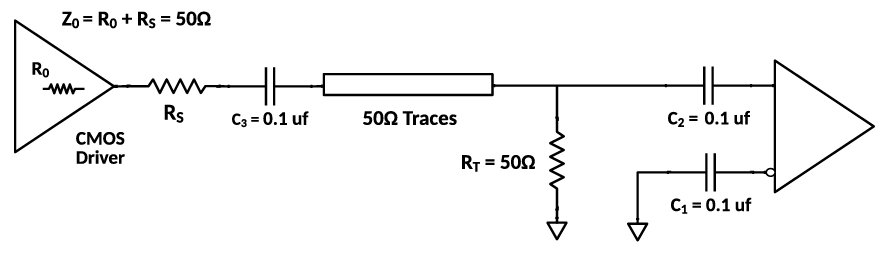

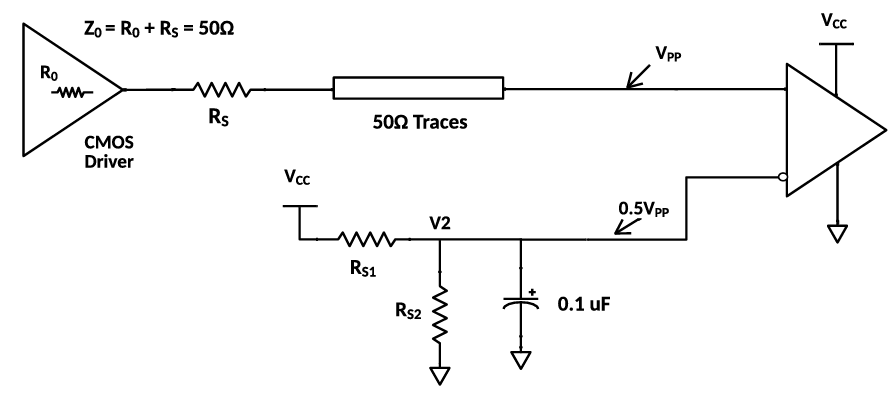

7.1. 使用 LVCMOS 驱动器驱动时钟输入(交流耦合)

对于大型单端输入信号,如 3.3 V 或 2.5 V LVCMOS,应在输入端附近放置一个 50 Ω 负载电阻,用于信号衰减以防止输入过载,并用于线路终端以尽量减少反射。单端输入压摆率应尽可能高,以减少性能下降。时钟输入的内部偏置电压约为 (VCC-0.3)/2 V,因此输入可以采用交流耦合,如图 4 所示。LVCMOS 驱动器加上 Rs 的输出阻抗应接近 50 Ω,以匹配传输线和负载终端的特性阻抗。

图 4 单端 LVCMOS 输入,交流耦合

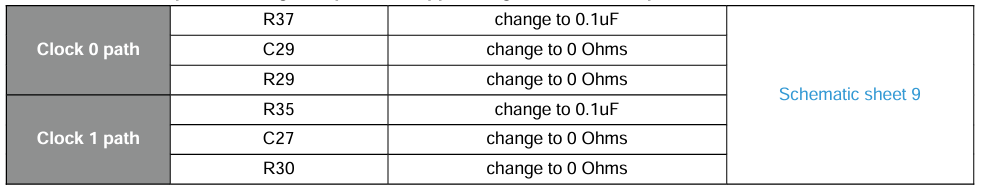

表 12 列出了电路板的变化。

表 12. 支持单端交流耦合 LVCMOS 所需的电路板组件更改

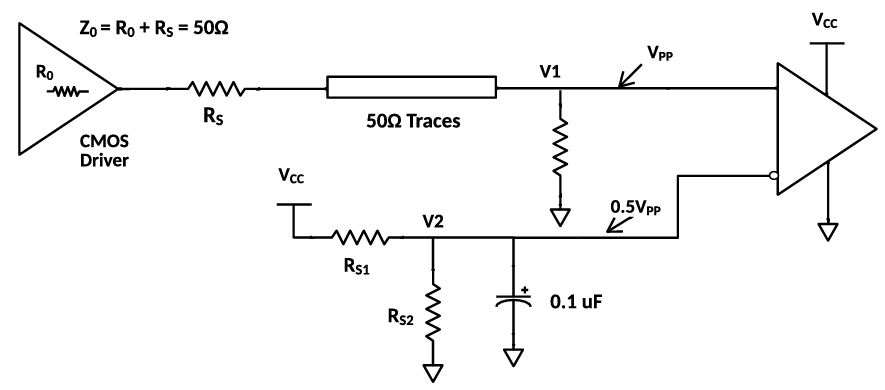

7.2. 使用 LVCMOS 驱动器驱动时钟输入(直流耦合)

单端时钟可以直流耦合到 SiT92211 缓冲器。如果要驱动 CLKin,则必须使用电阻分压器设置 CLKin* 电压,以匹配直流耦合单端时钟的共模。如图 5 所示。

图 5. 单端 LVCMOS 输入,直流耦合

案例 1: 让我们来看看一个 LVCMOS 驱动器(阻抗为 50 欧姆)驱动位于 SiT92211 输入端的 50 欧姆负载的情况。假设 LVCMOS 驱动器的电源电压为 1.8 V,则芯片输入端的时钟摆幅为 0.9 Vpp。我们要将基准节点的基准电压设置为 0.45 V。选择 VCC = 1.8 V,RS2=3RS1。RS1、RS2 应在千欧范围内。因此,如果我们设置 RS1=3 K,RS2=1 K。

表 13. 支持单端直流耦合 LVCMOS 所需的 EVK 电路板更改

案例 2: 如果负载为纯电容性负载,则 LVCMOS 驱动器的电源电压为 1.8 V。选择 VCC = 1.8 V,RS2=RS1。RS1、RS2 应在千欧范围内。因此,如果我们设置 RS1=1 K,RS2=1 K。

图 6. 单端 LVCMOS 输入,直流耦合电容负载

表 14. 驱动纯电容性负载的单端直流耦合

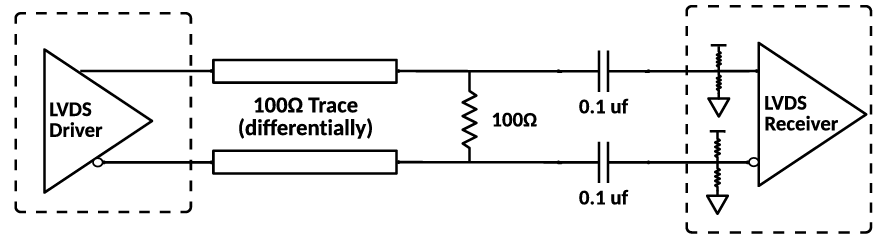

8 驱动差分 LVDS 或 LVDS 升压(交流耦合)

输入端有一个 100 欧姆的差分电阻,为 LVDS 或 LVDS 升压提供电流通路。100 欧姆差分信号由 0.1uF 的交流耦合电容跟随。因此无需改变电路板配置。

图 7. LVDS 或 LVDS 升压交流耦合

8.1. 驱动直流耦合 LVDS 的电路板配置

LVDS(直流耦合)

在尽可能靠近接收器的位置使用 100 欧姆差分端子。如图 8 所示。

图 8. 直流耦合 LVDS 的终端方案

8.2. 直流耦合 LVDS 所需的电路板改动

表 15 直流耦合 LVDS 或 LVDS 升压所需的电路板改动

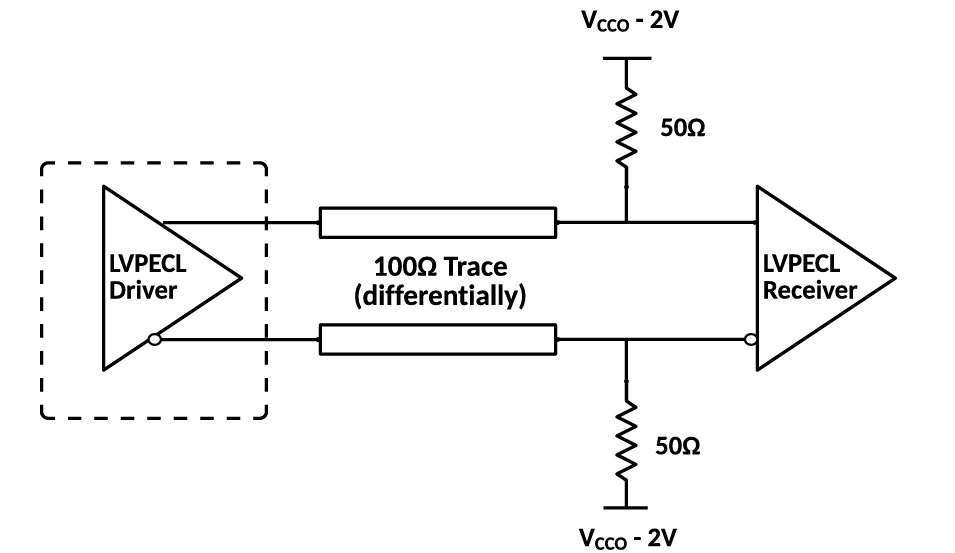

9 、驱动 DC/AC 耦合 LVPECL 所需的电路板配置

9.1. 直流/交流耦合 LVPECL

VPECL 标准要求输入时钟驱动器采用直流通路。接收器上的 50 欧姆端接采用 VCCO-2 V 偏置。VCM(VCC-2 V)需要能够承受或提供电流。可通过跳线 J4、J7 在输入时钟电路中提供 VCM。

因此无需更改电路板,只需通过跳线 J4、J7 提供 VCM。

图 9. 直流耦合 LVPECL

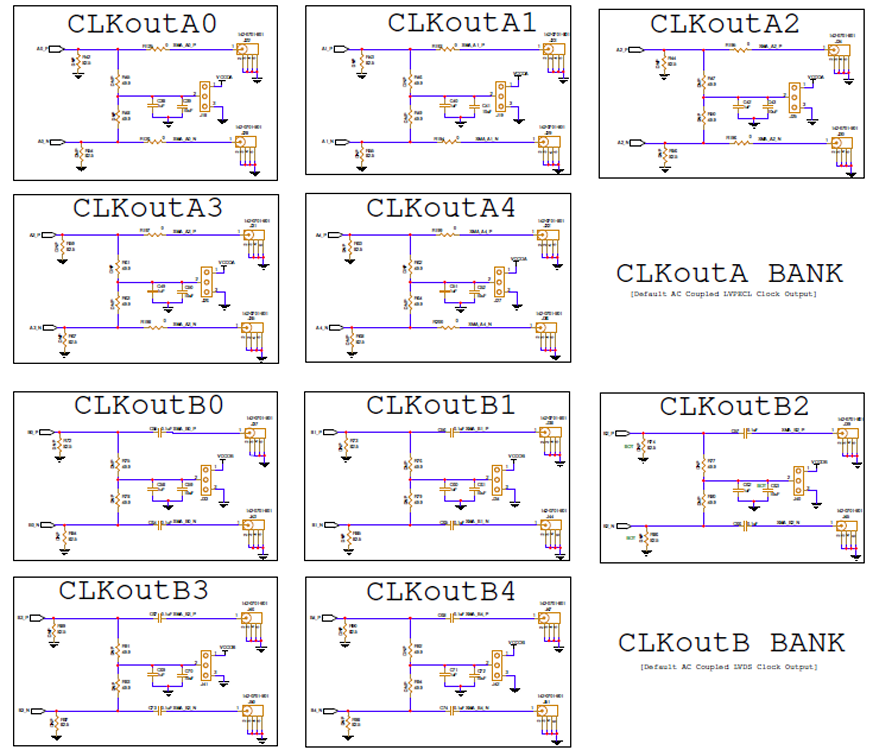

10 、输出配置

A 组输出默认配置为驱动 EVK 上的 LVPECL。A 组输出通过差分传输线和 0 欧姆电阻连接至 SMA 输出连接器。使用 LVPECL 配置时,应提供适当的 50 欧姆直流终端。

图 10. 用于 LVPECL 或 HCSL 的 A 组输出配置

B 组输出默认配置为驱动 EVK 上的 LVDS。B 组输出通过差分传输线和 0.1uF 交流耦合电容器连接至 SMA 输出连接器。使用 LVDS 配置时,应提供适当的 100 欧姆差分终端。

图 11. 用于 LVDS 的 B 组输出配置

EVK 快照

图 12 EVK 快照

如表 5 所述,模块 1 有 USB 端口,用于为电路板供电或选择跳线,以便使用外部电源供电。

块 2 具有跳线设置,用于配置芯片 VCC(如表 6 所示)。

如表 10 所述,模块 3 具有用于配置芯片 VCC_AUX 的跳线设置。

如表 7 所述,模块 4 具有配置芯片 VCCOA 的跳线设置。

模块 5 具有跳线设置,用于配置表 8 所述的芯片 VCCOB。

模块 6 的跳线设置用于配置芯片 VCCOC,如表 9 所示。

模块 7 的跳线设置用于选择 CLK_IN_SEL0、CLK_IN_SEL1、CLK_OUTA_TYPE0 和 CLK_OUTB_TYPE0,如表 11 所述。

模块 8 的跳线设置用于选择 REFOUT_EN 和 CLK_OUTA_TYPE1,如表 11 所示。

模块 9 的跳线设置用于选择 CLK_OUTB_TYPE1,如表 11 所示。

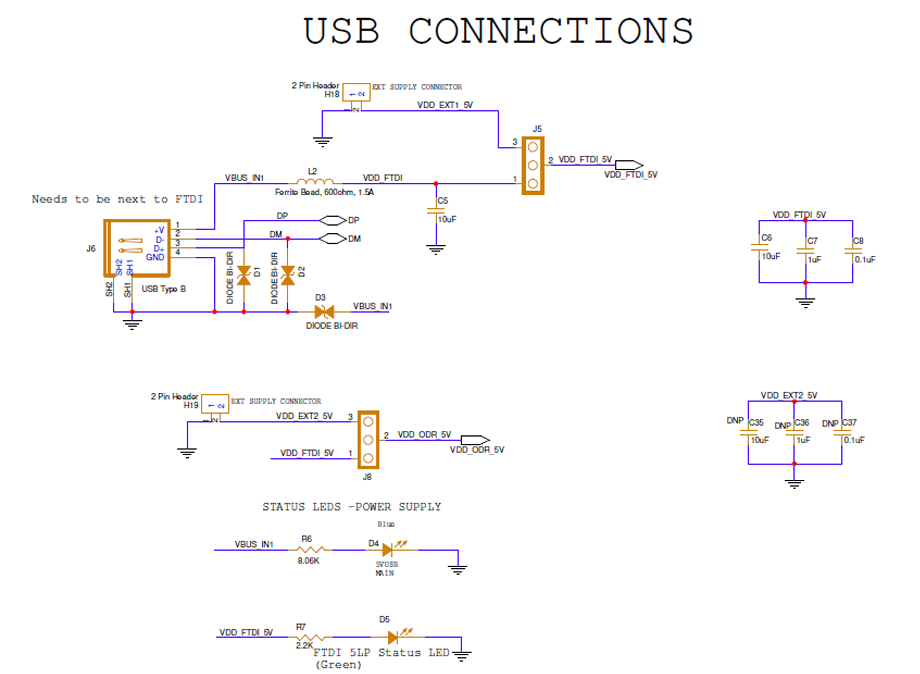

11 、SiT92211 评估套件示意图

11.1. 原理图 1

图 13. VCC 稳压器

11.2. 原理图 2

图 14. VCCOA 调节器

11.3. 原理图 3

图 15. VCCOB 调节器

11.4. 原理图 4

图 16. VCCOC 调节器

11.5. 原理图 5

图 17. VCC_AUX 稳压器

11.6. 原理图 6

图 18. 来自 USB 端口的主电源

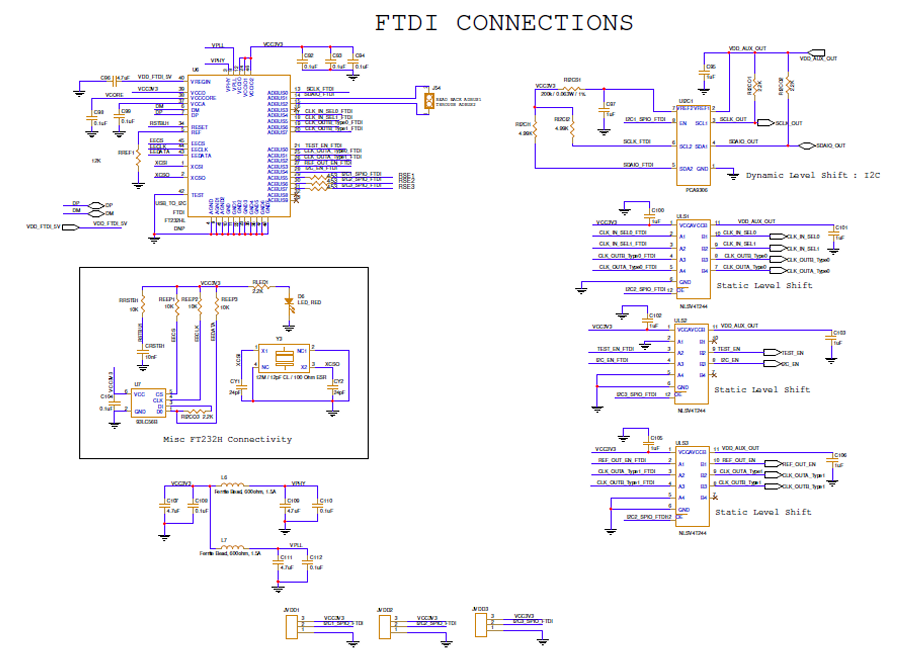

11.7. 原理图 7

图 19. 用于自动控制 GPIO 引脚的 FTDI 芯片

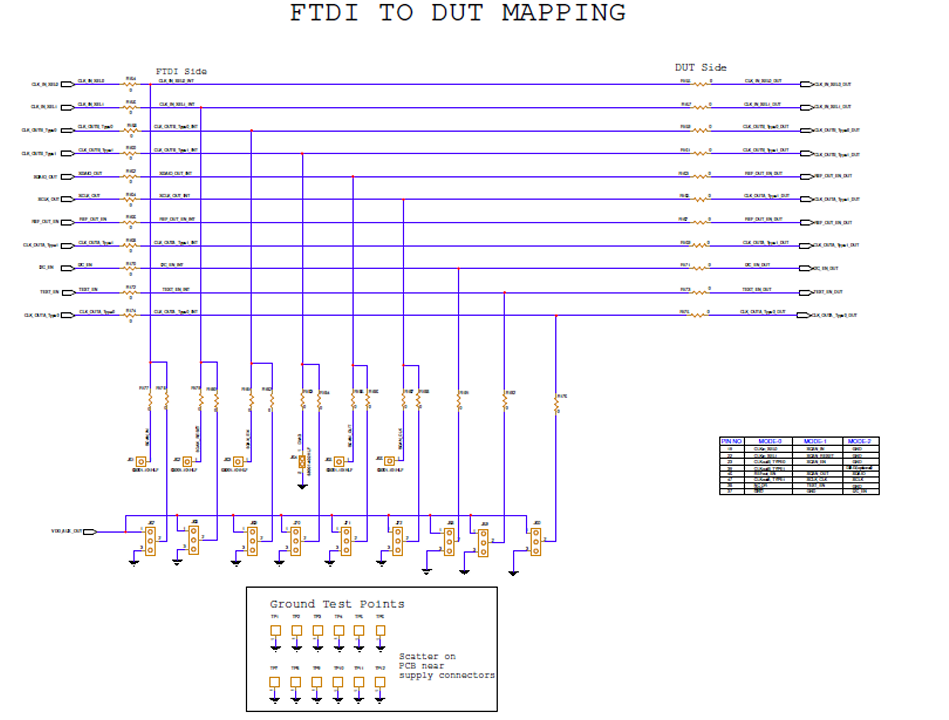

11.8. 原理图 8

图 20. FTDI 信号到 DUT 映射

11.9. 原理图 9

图 21. 输入时钟配置

11.10.原理图 10

图 22 输出配置 - A 组配置为 LVPECL/HCSL B 组配置为 LVDS

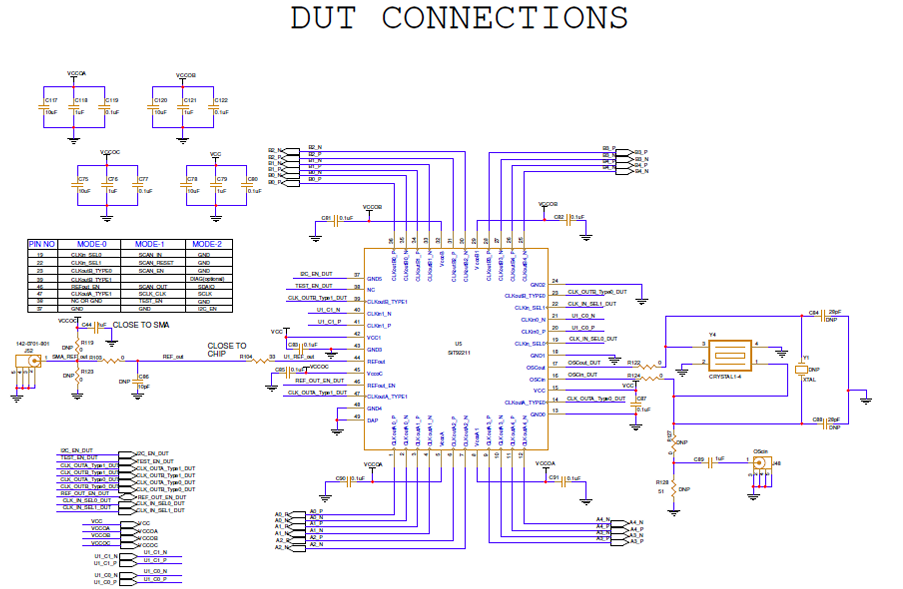

11.11.原理图 11

图 23. SiT92211 连接示意图

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483