汽车级晶振SiT1625如何应用于FPD-Link 高级驾驶辅助系统(ADAS)

1. 引言

FPD-Link 是由德州仪器开发的串行器 - 解串器(SerDes)接口,如今常用于信息娱乐和高级驾驶辅助系统(ADAS)应用。FPD-Link 将高清视频从摄像头传输到 ADAS 计算机,也将其从信息娱乐系统传输到液晶显示器(LCD)。它具有先进的技术,能够在恶劣的电磁干扰(EMI)环境中使用长电缆。

FPD-Link 于 1996 年推出,并历经了几代发展,最新一代是 FPD-Link IV。从 FPD-Link II(2006 年)开始,该接口专为汽车信息娱乐和摄像头接口应用而设计。FPD-Link III(2010 年)在同一差分对上增加了双向通信通道。此反向通道支持 GPIO 和 I2C 通信,以及上行时钟传输(见下文的同步时钟)。FPD-Link IV(2022 年)代表了最新一代。

2. FPD-Link 时钟要求

FPD-Link 需要一个由振荡器(如 SiT1625)提供的 25 MHz 至 100 MHz 之间的单端 LVCMOS 时钟(称为“PCLK”)。时钟抖动必须得到良好控制。时钟上过多的抖动会“关闭眼图”,导致链路上的位错误率(BER)增加。有关抖动及其对高速串行链路影响的更多详细信息,请参阅产品培训。

FPD-Link 有两种基本的时钟架构:异步和同步。本文将从时钟角度探讨这两种架构。讨论每种架构的总体优缺点不在本文的范围之内。有关此主题的信息,请参阅产品培训。

设计人员的关键考虑因素有: • 可靠性 • 抖动性能 • 电磁干扰(EMI)和电磁兼容性(EMC)合规性 • 小尺寸

3. 异步 FPD-Link 架构

异步模式代表了驱动串行数据接口的传统方式:时钟和数据都在串行器的输入端提供。传输后,时钟和数据都在解串器端被恢复。由于多个独立的链路各自使用其独立的时钟运行,所以此模式被称为异步。

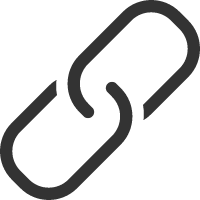

图 1:异步 FPD-Link 方框图 PCLK 时钟

FPD-Link 串行器提供了向成像器输出时钟的可能性,如图 1 所示。另一种用例是用振荡器驱动成像器,并将成像器时钟作为串行器的输入。TI 学习中心[4]对此模式有更详细的解释;然而,此用例存在串行器 PCLK 输入上抖动较大的缺点,因此可能会增加链路上的误码率。每当需要异步模式时,SiTime 建议直接将 PCLK 从振荡器提供给串行器(如图 1 所示)。

4. 同步 FPD-Link 架构

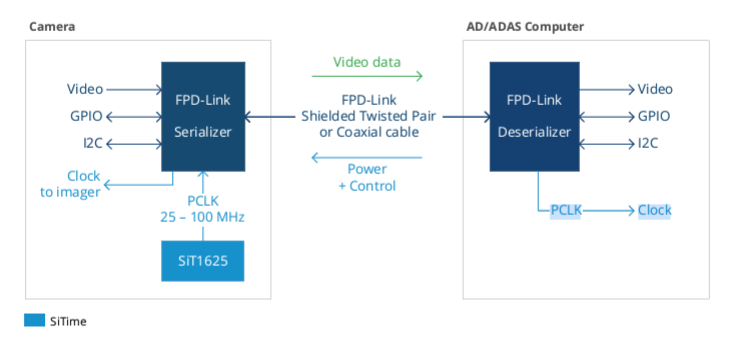

在同步模式下,时钟由振荡器提供给 FPD-Link 解串器端。然后时钟通过 FPD-Link 反向通道“上行”传输到串行器。此模式被称为同步,因为链路与解串器同步运行,因此多个链路因此而同步。但是,同步多个链路需要额外的步骤:所有解串器的时钟必须具有相同的频率和相位。这最好通过时钟发生器来实现(见第 5 节)。

图 2:同步 FPD-Link 方框图

根据德州仪器(TI)学习中心[4],同步模式相对于异步模式的主要优势在于:

• 降低物料清单(BOM)成本:摄像头模块上无需振荡器。取而代之的是,解串器端需要一个时钟源。从系统级的角度来看,这是否相互抵消?未必。因为 AD/ADAS 计算机需要多个时钟,通过将多个振荡器整合为一个时钟发生器,有很大的改进潜力。

• 降低电磁干扰(EMI):在异步模式中,多个独立的 FPD-Link 以相似但不完全相同的频率进行时钟控制。这可能会产生许多低频混合杂散。同步时钟解决了这个问题——这里再次强调,前提是所有时钟都来自单个源,例如时钟发生器。

• 提高可靠性:引用 TI 学习中心[4]的话,“在摄像头的可靠性方面,晶体振荡器通常是薄弱环节之一。”这再正确不过了。但为什么解串器端的晶体振荡器会比串行器端的晶体振荡器更可靠?可靠性问题的答案是用更好的东西取代晶体振荡器(或基于晶体的时钟发生器)。SiTime 基于 MEMS 的定时设备的可靠性比基于晶体的振荡器高达 50 倍。

5. 使用 SiTime 时钟发生器同步多个 FPD-Link 链路

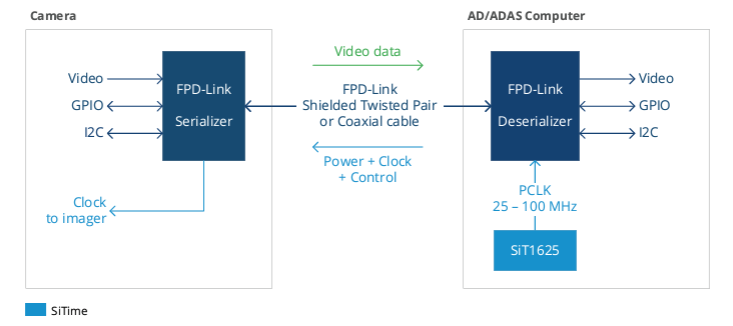

当多个摄像头(例如车辆的左前、前中和右前)被同步时,它们的帧会对齐。这减少了 ADAS 计算机端对 RAM 缓冲区的需求,否则就需要重新对齐不匹配的视频帧。

图 3:多个同步的 FPD-Link 链路

所有时钟具有相同的频率和相位是同步多个链路的先决条件。这最好通过时钟发生器来实现。SiTime 汽车时钟发生器具有集成的、高可靠性的 MEMS 谐振器。多个可配置的输出频率使具有不同频率的 FPD-Link 链路成为可能。典型的用例是具有不同分辨率的多个摄像头。ADAS 应用的高级功能也可用。有关详细功能集和产品可用性的信息,请联系 SiTime。

通过单输出 SiTime 振荡器的时钟,并通过扇出缓冲器进行分配来为多个 FPD-Link 链路提供时钟也是可行的,并且不会影响可靠性。然而,在这种情况下,以不同频率运行链路是不可能的。扇出缓冲器也会增加时钟抖动。SiTime 建议在需要多个时钟(相同或不同)时使用时钟发生器。

6. EMI 降低

由于 FPD-Link 旨在在易受电磁干扰(EMI)的环境中运行,因此必须小心确保最佳的 EMI/EMC 合规性。除了电路和 PCB 设计的常规最佳实践外,还可以通过使用具有可调节驱动强度的振荡器(通过时钟的可配置上升/下降时间)来降低 EMI。

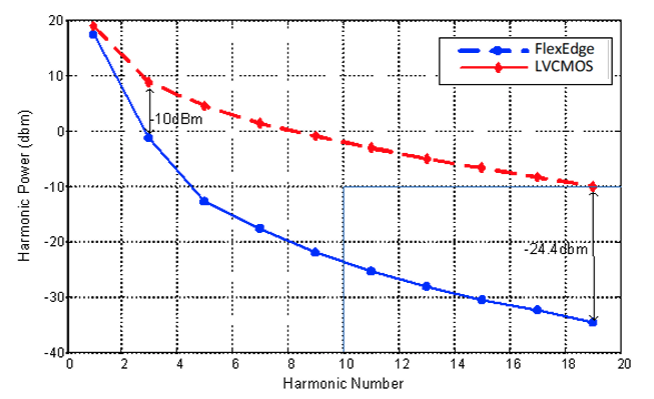

诸如 SiT1625 之类的设备包含可编程驱动强度功能。减慢上升/下降时间可将谐波功率降低至 -24.4 dB(图 4)。请注意,边缘速率减慢太多会增加抖动,这可能对链路的误码率(BER)有害。抖动必须保持在规定的限度内。

带 FlexEdge™ 输出的 SiTime LVCMOS 振荡器在 VDD = 3.3 V 时的奇次谐波功率比较

图 4:减慢上升/下降时间可改善时钟谐波的辐射 EMI

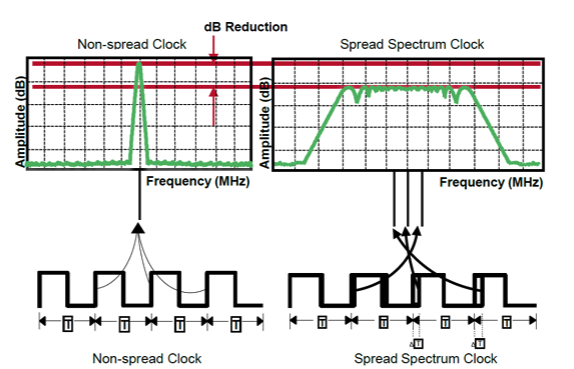

图 5:无论处于同步还是异步模式,扩频时钟都将峰值载波能量

分布在更宽的频率范围内,FPD-Link 与用于降低 EMI 的扩频时钟(SSC)兼容。SSC 将载波能量在宽频谱上展开,从而降低其峰值幅度。SSC 通常由 FPD-Link 芯片组生成。某些 SiTime 设备,如 SiT9025,有可能在内部生成 SSC 调制。

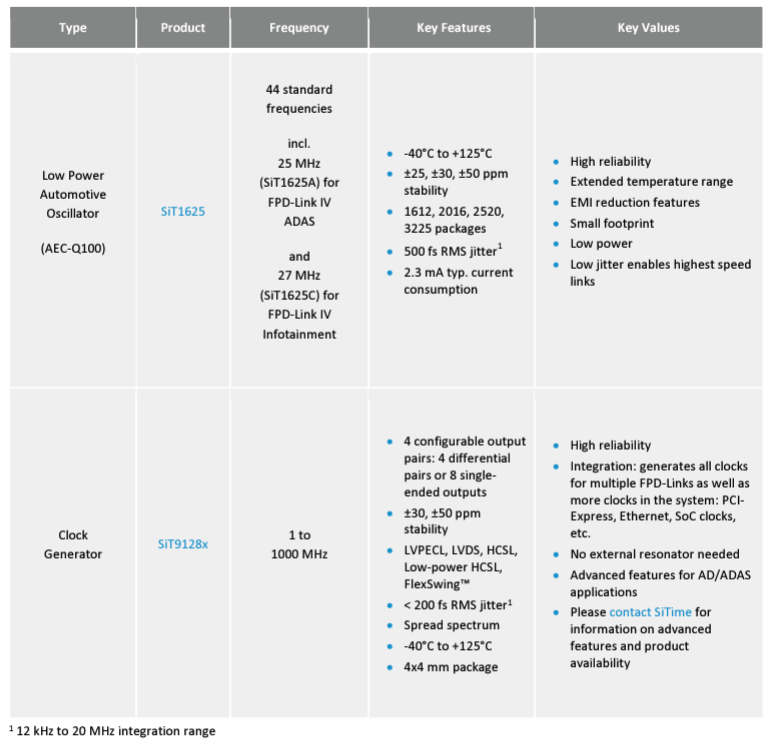

7. 特色 SiTime 产品

8. SiTime 优势

与石英晶体相比,所有 SiTime 设备都具有以下优势,这些优势对于汽车应用尤为重要:

• 可靠性高达 50 倍以上:除了减少现场故障数量外,更高的可靠性还意味着更低的 FIT 率。这在 FMEDA(故障模式影响及诊断分析)中提供了更好的硬件安全指标,这是功能安全评估所需的定量分析的一部分。

• 抗冲击、抗振动和抗电磁干扰能力高达 100 倍以上:由于 MEMS 谐振器的尺寸(0.4×0.4 毫米)较小且质量低于晶体。

• EMI 降低特性:驱动强度选择、扩频时钟

厂商技术支持

厂商技术支持 收藏网址

收藏网址 400-888-2483

400-888-2483