汽车级晶振

单端

差分

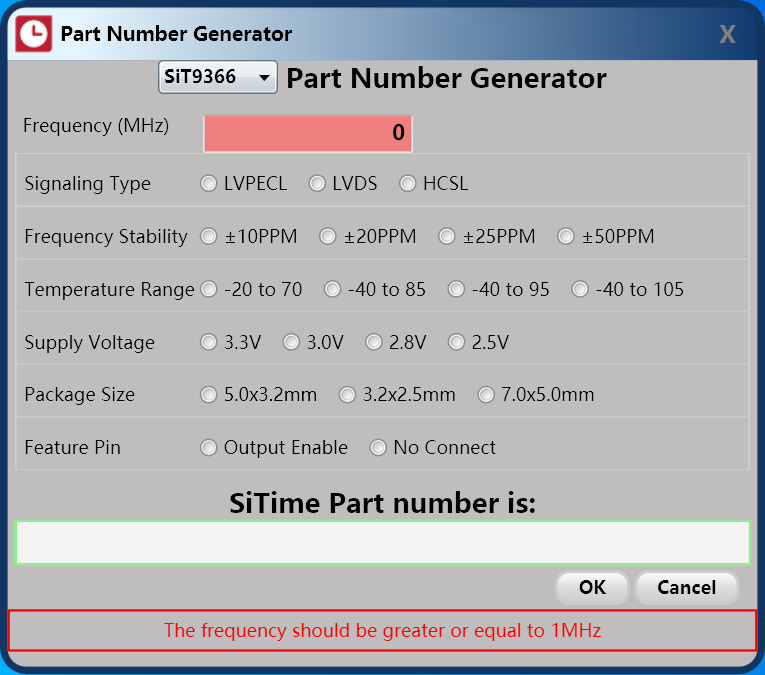

SiT9386

1-220MHz任意频率,AEC-Q100,汽车级差分晶振LVPECL/LVDS/HCSL

SiT9387

-40~105℃,220-725MHz任意频率,LVDS/LVPECL/HCSL差分信号

SiT9396

-40~125℃,1-220MHz任意频率,LVDS/LVPECL/HCSL差分信号

SiT9397

-40~125℃,220-920MHz任意频率,LVDS/LVPECL/HCSL差分信号压控晶振VCXO

单端

0.23ps低抖动差分

SiT3372

1-220MHz任意频率,HCSL/LVDS/LVPECL,最大±3200ppm牵引范围

SiT3373

220-725MHz任意频率,HCSL/LVDS/LVPECL,最大±3200ppm牵引范围低成本差分

高精度温补晶振TCXO

±0.5ppm~2.5ppm

±0.1ppm~0.25ppm

SiT5501

1-60MHz任意频率,±0.01ppm高精度,支持压控、数控、方波、削峰正弦波多种功能可选±5ppm温补差分

从 RMS 抖动测量中去除示波器噪声

1 简介

我们在此介绍了一种新方法,可在来自测量环境的信号中添加的抖动水平接近或超过信号的固有抖动时,使用实时示波器准确测量抖动。 该方法建立在之前的工作的基础上,该工作结合了测量和建模数据以消除峰峰值抖动数据中的虚假杂散。 我们在此重点消除测试环境在 RMS 抖动数据中引入的随机幅度噪声。

测试环境可以向被测信号 (SUT) 添加相位和幅度噪声。相位噪声直接调制信号的边沿,而幅度噪声在示波器采样过程中转换为相位误差。这两种情况都将测得的 SUT 抖动增加到其真实值以上。也许测试环境中幅度噪声的主要来源是示波器采样系统中的垂直(量化)噪声。这可以在设置示波器时进行优化,但在某种程度上始终存在。示波器交错架构中的缺陷还会增加幅度噪声,从而使测量波形失真。来自测试环境的其他幅度噪声源可能包括巴伦、EMI、串扰、电源线噪声等,它们可以在示波器外部的 PCB 或连接器级将噪声注入 SUT。尽管使用以下方法可以消除许多这些随机幅度噪声源,但它无法消除测试环境引入的相位噪声,例如来自示波器内部振荡器的相位噪声。

下面的方法与上面的后一种方法有些相似,但依赖于经验建模,而不是数据表方程,来校准测试环境贡献的抖动。我们将通过示例介绍这种方法,使用它来评估 PCIe® v4.0 是一种实际应用,因为 :

(2) 每一代新规范都有更低的时钟抖动要求

(3) 示波器的本底噪声接近或超过当今精密振荡器的噪声本底

(4) PCI Express®市场对成本敏感,这阻碍了为时钟性能报告时钟抖动(例如,rmance 和 (5) 准确无环境噪声)支付过高的费用,可以增加时钟供应商提供的解决方案数量,从而为其客户提供更多选择和灵活性。

尽管下面的讨论评估 PCI 方法通常可用于消除 SIG® 参考时钟的时间间隔误差 (TIE) 抖动、来自时钟或数据信号的任何抖动或电压测量的(随机幅度)环境噪声。

2 方法论

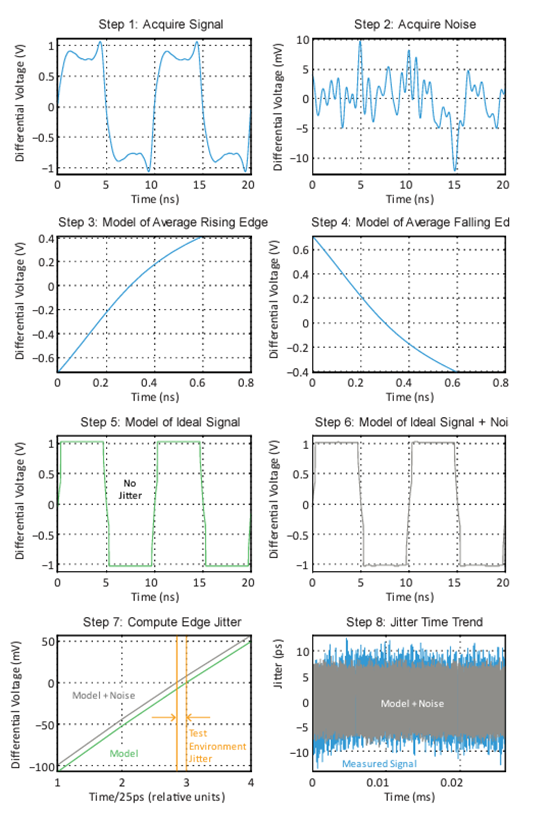

该方法由几个关键步骤组成,在下面讨论并在图 1 和图 2 中说明。请注意,某些步骤可以以一种或多种方式(未显示)执行并获得类似的结果。

步骤1:获取信号。 为被测设备 (DUT) 通电并将其配置为输出 SUT。 对于 PCIe® v4.0 应用,一致性负载板连接在 DUT 和示波器之间(在 4 GHz 时有 15 dB 的损耗,2 pF 端接和到示波器的探头连接)。 设置实时示波器来测量抖动,并对 SUT 执行一次连续采集。 对采集的电压波形应用降噪滤波器(通常为 2-5 GHz,取决于信号的边缘速率)以去除宽带示波器噪声。

步骤2:获取噪声。 要从测试环境中消除尽可能多的抖动,请关闭 DUT 并将其连接到示波器。 要消除仅示波器抖动,请关闭 DUT,将其与示波器断开连接,并终止示波器输入。 使用与步骤 1 相同的示波器设置采集波形。此波形代表要消除的测试环境中的噪声。 对这个噪声波形应用步骤 1 滤波器。

步骤3:平均上升沿模型。 检测信号波形中上升沿的位置。 使用每个边沿的中点交叉电压(例如,差分信号为 0V)作为其原点,为代表平均上升沿的时间段创建连续时间模型。 该模型的电压范围只需要扩展到足够远,以便将噪声波形添加到模型中的这个位置不再改变波形中点附近的数据点(这是计算抖动的唯一数据点)。

步骤4:平均下降沿模型。 对下降沿执行步骤 3。

步骤5:理想信号模型。 模拟在相同时间间隔采样的离散方波(或其他)波,并且具有与信号波形大致相同的幅度。 使用上升沿和下降沿模型替换方波模型对应边沿的点,使模型和信号波形的平均周期在机器精度范围内一致(例如,浮点精度为16位以上)。 这产生了理想的无抖动信号模型(在机器精度范围内),其 0V 过渡区域遵循其各自边缘的平均形状。 将仅使用此模型的中点(例如,0V)交叉区域。

步骤6:理想信号 + 噪声模型。 添加噪声和理想模型波形以创建模型加噪声波形。

步骤7 和 步骤8:计算边缘抖动; 抖动时间趋势。 按照传统方式计算信号波形中每个边沿的时间间隔误差 (TIE) 抖动,以获得信号波形的抖动时间趋势(图 1 中的蓝色波形,步骤 8)。 重复模型加噪声波形,使用理想模型波形作为参考(如图 1 步骤 7 中的一个上升沿所示;以及图 1 步骤 8 中的灰色波形)。

图 1:从示波器抖动数据中去除环境噪声的关键步骤图示

步骤 9:过滤抖动频谱。 将抖动时间趋势转换到频域,并对每个趋势应用相同的所需抖动滤波器。 示例频谱如图 2 所示。

图 2: (1) 测量的信号(蓝色)和 (2) 理想(无抖动)信号的经验模型以及测试环境中添加的噪声(灰色)的滤波抖动频谱

步骤 10:计算 RMS 抖动。 将滤波后的抖动频谱转换回时域。 计算滤波信号 (JS) 和滤波模型加噪声 (JN) 的 RMS 抖动。 估计 DUT 的真实固有 RMS 抖动为:

步骤11:计算误差线。 计算计算出的 DUT 抖动的误差线。 这些条形表示从噪声去除过程中估计 DUT 抖动 (JDUT) 的不确定性。

3 结果

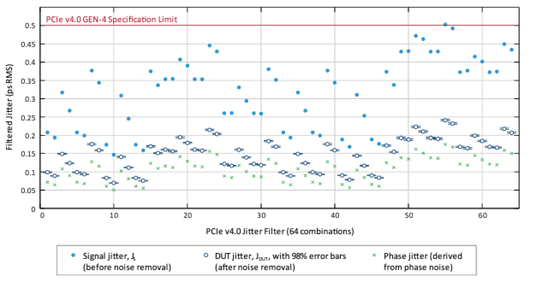

图 3 比较了所有 64 个 PCIe® GEN-4 抖动滤波器组合在从测试环境中去除噪声之前 (JS) 和之后 (JDUT) 的抖动结果。 在 DUT 抖动数据上绘制误差线以表示 98% 的置信区间。 图 3 中最坏情况的滤波器组合如上图 2 所示。

图 3:计算的 PCIe v4.0 GEN-4 抖动结果,比较所有必需的滤波器组合之前和之后噪声去除。 作为参考,还显示了相位抖动

使用传统分析(例如 JS),上面分析的时钟设备未通过 PCIe® v4.0 GEN-4 合规性抖动限制 0.5 ps RMS。 但是,在消除测试环境引入的抖动后,设备(例如 JDUT)很容易通过。

PCI-SIG® 协会假设参考时钟抖动几乎都是随机的 [11],并且在不去除杂散(GEN-4 SSC 杂散除外)的情况下计算 RMS 抖动。 实际上,可以存在一定量的确定性抖动而不会对结果产生太大影响,因为 RMS 计算对异常值具有相当的容忍度。 为了遵循当前的 PCIe® v4.0 实践,用于创建图 3 的频谱并未专门去除这些杂散。 然而,一般而言,在计算打算表示随机抖动的 RMS 值时,应去除所有显着的杂散。 或者,当打算包括 RMS 抖动的所有统计成分时,应保留杂散。 后一种情况在电信市场(例如 SONET)中很常见,而前者在非电信市场(例如以太网)中很常见。

作为参考,器件的相位噪声也被测量、过滤、积分并绘制为图 3 中的相位抖动。作为完整性检查,观察 DUT 抖动 (JDUT) 大于每个滤波器组合的相应相位抖动。 实际上,相位抖动是 DUT 抖动的下限。 与相位抖动相比,图 3 中的 DUT 抖动可能更大,原因是来自示波器采样时钟的相位噪声和上述杂散噪声(在存在杂散的范围内)。

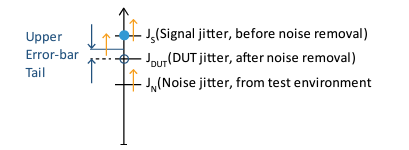

4 误差棒

附录中提供了噪声去除过程的统计模型和形式分析。 它假设设备抖动 (JDUT) 和环境噪声 (JN) 是独立的、不相关的和正态分布的。 下面将讨论其一些有趣的结果。

图 4 说明了 DUT 抖动的上部误差条如何随着测试环境中抖动 (JN) 的增加而变化(请注意,下部误差条易于绘制,但在确定合规性方面没有作用,因此在我们的分析中基本上被忽略了) . 例如,可以将图 4 视为图 3 中所示的过滤器组合之一。

图 4:在 JUST 固定的情况下,增加 IN 会导致上误差条(和 JS)增加

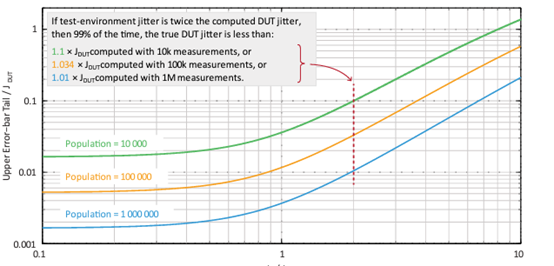

图 5 显示 98% 的上误差条随 JN 增加,但随着抖动测量值的增加而减少。 为了概括图 5,轴被归一化为计算出的 DUT 抖动(例如,在去除噪声之后)。 图 5 中还包含了对图表数据的示例解释。请注意,98% 的误差上限将 99% 的总人口限制在其下方。

图 5:通过正确选择总体,JDUT 的 98% 误差条可以变得微不足道

在极端情况下,传统上使用示波器测量的 RMS 信号抖动 (JS) 恰好等于测试环境添加的 RMS 抖动 (JN)(例如,想象图 2 中的灰色和蓝色曲线具有相同的 幅度),则通过正交减法计算的 DUT 抖动为 0。 尽管如此,如果分析了足够多的样本,则计算出的 DUT 抖动上的误差线会保持相对较小。 例如,如果 JS = JN = 7.3 ps RMS 具有 1M 样本,则 JDUT = 0 数据点上的 98% 上误差条位于 497 fs RMS,正好满足 PCIe® v4.0 GEN-4 0.5 ps 的要求 有效值。 实际上,测试环境引入的抖动(例如示波器垂直噪声)通常要低得多。 例如,图 3 中最坏情况的滤波 JN 低于 0.5 ps RMS。 因此,该方法可以以高置信度实际应用于嘈杂的环境。

请升级

400-888-2483

400-888-2483 我的账户

我的账户